低压动态无功补偿装置设计说明

现代低压电网中,感性负荷和冲击性负荷占相当大的比重,造成电网功率因数降低,电能质量严重恶化。究其根本原因是用电负荷工作中无功功率需求量的急剧变化。因此,急需开发一种能快速响应电网无功需求,进行实时跟踪补偿的无功补偿装置。目前无功补偿装置中,采用机械开关(接触器或断路器)或复合开关投切电容器的装置,其响应速度慢,不能实现对无功功率的动态补偿;而采用晶闸管投切电容器的装置,其控制器多为单CPU结构,控制精度和速度难以同时保证。

本文介绍的快速型低压动态无功补偿装置针对电网负荷的快速变化,以DSP芯片作为核心控制器,配合FPGA驱动大功率晶闸管投切电容器。由于采用了无触点开关过零投切技术,电容器的投切均可实现无过渡过程的平稳投入和退出。因此,本装置控制精度高(无功功率2级,功率因数0.5级),响应速度快,响应时间不大于13ms,而且可以频繁地投切动作,能有效地跟踪补偿快速变化的负载,改善电能质量。

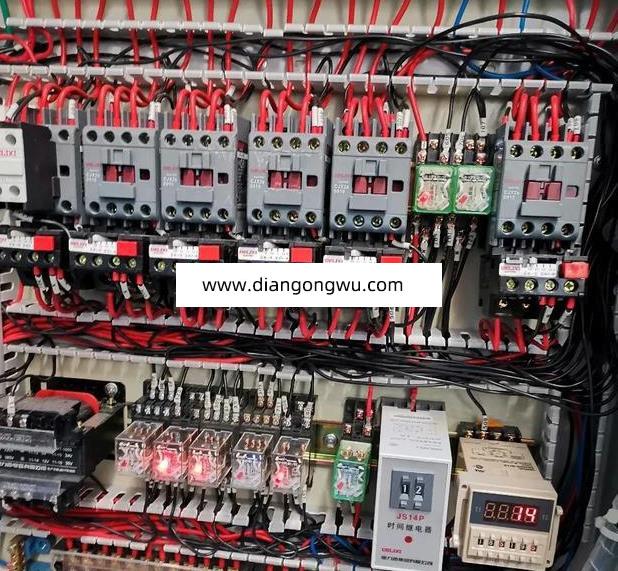

1 主电路设计

本装置的电容器按照8:4:2:1原则分成四组,可实现15级组合,这种不等容分组方式的优点是利用较少的分组可以得到较小的补偿级差。控制电容器投切的无触点开关由两只单向晶闸管反向并联构成。当晶闸管施加正向电压,且门极有脉冲触发信号时,晶闸管导通,电容器投入电网。当触发脉冲信号去掉后,电流过零或反压时,晶闸管截止,电容器从电网上切除。这种两只晶闸管反向并联结构与一只晶闸管和一只二极管反并联结构相比,具有投切速度快,晶闸管承受电压低的优点。另外晶闸管上并联有RC吸收电路,用于吸收浪涌电流和抑制过电压。每一电容支路串联一定容量的电抗器,配置电抗率<0.5%(有时到0.01%~0.02%)的电抗器,主要目的是限制电容器的合闸涌流;配置电抗率为4.5%或6%的串联电抗器,可抑制5次以上的谐波电流;配置电抗率为12%~13%的串联电抗器,可抑制3次以上的谐波电流。

电容器采用△形接线方式,反向并联晶闸管采用接在△内部的接法。这种接法的最大优点是流过晶闸管的电流是其它接线方式的,这样可以有效的降低晶闸管的发热量。同时这种接法对3次谐波也有抑制作用,对电网不会造成污染[2]。晶闸管的耐压值一般按计算,其中K1为电压欲度,一般取1.1~1.2,K2为电网电压波动系数,一般取1.15,U为电网线电压。晶闸管的电流一般按,其中C为电容容量,单位为μF。

2 控制系统设计

2.1 控制系统硬件设计

控制器采用DSP+FPGA的双CPU结构。电网电压电流信号经信号调理电路调理后送入DSP的模数转换器(ADC)。DSP对数据进行采集、处理后得到电网的无功功率、功率因数等物理量,然后根据检测值的大小以及设置值的大小,产生需要补偿的电容器组二进制代码。FPGA接收到此代码后,根据同步信号产生高频驱动脉冲。高频驱动脉冲经光耦隔离送至脉冲变压器,最后脉冲变压器驱动相应的晶闸管导通,电容器投入电网。

在整个系统中DSP采用TI公司的TMS320F2812,其工作频率可达150MHz,并且内部集成12位ADC,能够实时跟踪系统参数的变化,迅速完成投切判断,发出控制命令;并且DSP实时检测系统各种保护信号,完成故障判断并处理缺相、过压、过流、超温、晶闸管短路、晶闸管断路等故障,保障系统安全、稳定、快速地运行。FPGA内部主要设计了五个功能模块:高频驱动脉冲发生器、同步信号发生器、锁相环、51单片机和双口RAM。锁相环主要是确保DSP的采样精度,避免频率波动时的采样误差;51单片机主要完成按键处理、液晶显示和串口通讯等功能;双口RAM用于实现单片机和DSP间的数据交换。FPGA各功能模块具有并列运行的特点,能够迅速响应DSP发来的各种信息。

2.2 控制策略

我国电力行业标准中,按控制物理量不同,低压无功补偿控制器可分为四类:无功功率、无功电流、功率因数、复合型(按两个及以上物理量组合)。为了能最大限度地利用补偿设备提高电网的功率因数,不发生过补偿,无投切振荡,无冲击,反应灵敏、迅速,保证电压不超限,本装置以无功功率、电压、电流和功率因数综合判断作为投切电容器组的主要判据。