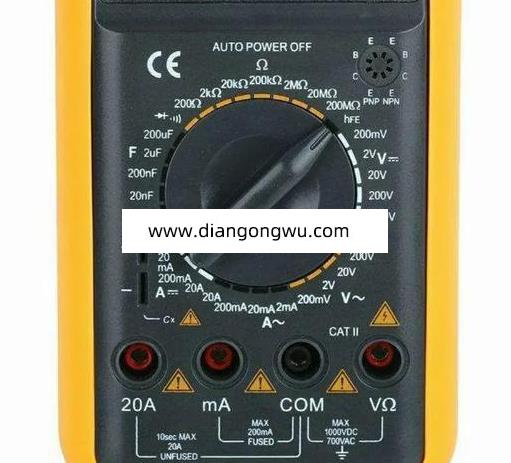

随着电子技术的发展和变化,对电路测量的要求也变得更高,在电子制作中会发现对很多参数的测量已不是一块万用表所能胜任的了, 比如单片机某I/O口的输出波形或制作放大器测其频率响应等等。所以,示波器自然而然地与万用表一样,变成了电子工程师和爱好者的必备工具

工作原理及结构介绍

数字示波器系统的硬件部分为一块高速的数据采集电路板。它能够实现双通道数据输入,每路采样频率可达到60Mbit/s。从功能上可以将硬件系统分为:信号前端放大(FET输入放大器)及调理模块(可变增益放大器)、高速模数转换模块(ADC驱动器、ADC)、FPGA逻辑控制模块、时钟分配、高速比较器、单片机控制模块(DSP)、数据通讯模块、液晶显示、触摸屏控制、电源和电池管理和键盘控制等几部分。

输入信号经前置放大及增益可调电路转换后,成为符合A/D转换器要求的输入电压,经A/D转换后的数字信号,由FPGA内的或者采集存储器FIFO缓存,再经通讯接口传输到计算机中,供后续数据处理,或直接由单片机控制将采集到的信号显示在LCD幕上。

可参考器件如下

在这几部分中,最重要的是程控放大(衰减)电路和A/D转换电路,因为这两个电路是数字示波器的咽喉,程控放大(衰减)电路决定了示波器的输入带宽和垂直分辨率,A/D转换电路决定了示波器水平分辨率,这两个分辨率直接决定着一个示波器性能的优劣。这两部分电路将被测信号转换成后面的处理电路所需的数据信号,这部分电路都可用高性能的集成电路加少量外围器件构成,电路设计简单,调试也很简单。整个示波器最难的应该是程序,也就是软件方面。软件承担着数字示波器的所有数据处理和控制任务,包括A/D采样控制、水平扫速控制、垂直灵敏度控制、显示处理、峰峰值测量、频率测量等任务。可以采用现在市面上很常见的单片机作为微处理器,使用C语言编程来实现。

程控放大(衰减)电路与电源电路

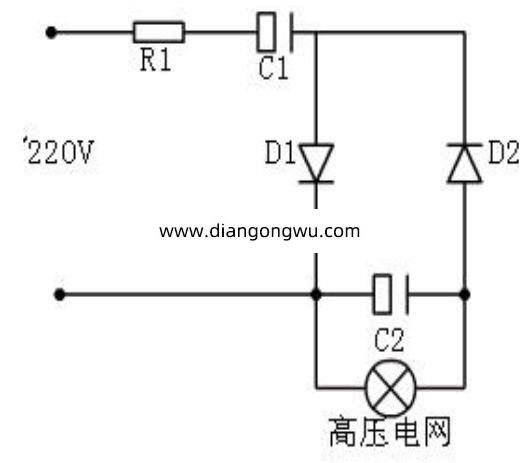

信号由常见的X10X1示波器探头输入,进入放大(衰减)电路。程控放大(衰减)电路的作用是对输入信号进行放大或衰减调整,使输出信号电压在A/D转换器输入电压要求范围内,达到最好的测量与观察效果,所以程控放大器电路在规定带宽内的增益一定要平坦。由于示波器电路上包含数字和模拟两个部分,为了避免相互干扰所以将数字部分的供电和模拟部分的供电分开,分别提供一组±5V的直流电源,并用电感与电容做成的滤波器隔离

Flash闪存与时钟电路

因为A/D转换器捕获的信号数据量较大,单片机内部的闪存不够使用,所以电路可选用一些外存使

用,同时,也作为写LCD的缓存使用。为了得到基准时钟信号,单片机还连接一块晶振,用来计算外部波形信号的实际频率。

FPGA控制单元

可编程逻辑器件FPGA是一种半定制的ASIC,它允许电路设计者自行编程实现特定应用的功能。本设计采 用了原理图输入和VHDL语言输入两种不同的方法,控制单元承载了大部分控制任务,为各个功能模块提供相应的控制信号以确保整个系统工作的正确性。具体实现如下几个方面的功能: 分频电路及产生A/D转换器的控制信号 本数据采集系统,具有比较宽的测量范围,在FPGA内部设计了一个分频电路,用来实现针对不同频率的被测信号选择不同的采样频率,确保采集数据更加精确。分频单元采用图形输入方法实现其内部结构图如图4所示。在图4中,利用T触发器在输入为1时,每个时钟沿到来时输出会发生跳变来实现分频的。同时我们可以看出,T触发器的输入是有一些逻辑组合构成的,这就构成了门控时钟。对于门控时钟,仔细分析时钟函数,以避免毛刺的影响。而门控时钟在满足以下两个条件时,则可保证时钟信号不出现危险的毛刺,门控时钟可以像全局时钟一样可靠的工作。

对于本设计中的A/D转换器,其控制信号只有两个:时钟输入信号CLK和使能输出信号OE。CLK信号直接通过有源晶振输入60M的信号,而OE信号则通过FPGA内部将和CLK同频同相的时钟信号反相后得到,这样刚好可以满足A/D转换器的转换时序关系。

高速A/D转换;电路

数字示波器中最重要的电路是A/D转换电路,它的作用是将被测信号采样并转换成数字信号存入存储器,说它是数字示波器的咽喉一点也不为过,因为它直接决定着数字示波器所能测量的最高频率,根据奈奎斯特定理,采样频率至少是被测信号最高频率的2倍才能复现出被测信号。而在数字示波器中采样频率至少应该是被测信号频率的5~8倍才行,否则根本观察不到信号的波形。