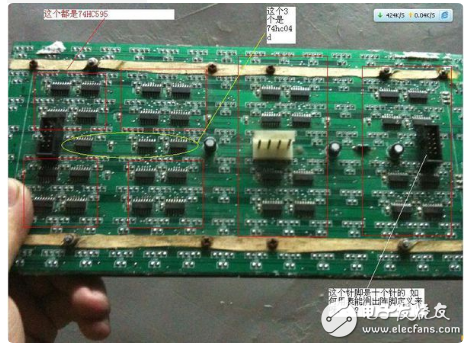

今天小编要和大家分享的是74hc138,电路图相关信息,接下来我将从74hc138灌电流有多大?基于74hc138的4个输入8个输出的逻辑电路图设计,本电路由74hc04d和adm483ear及max02ecpe等元件构成.这几个方面来介绍。

本电路由74hc04d和adm483ear及max02ecpe等元件构成.

74hc138是大家比较熟悉的元器件,那么关于它你真的了解吗?本文将讲主要探讨74hc138灌电流有多大以及基于74hc138的4个输入8个输出的逻辑电路图设计。

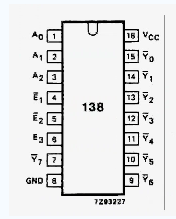

74hc138介绍

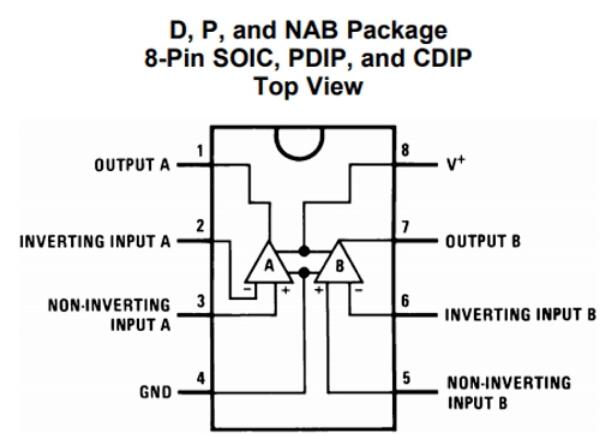

74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。74HC138译码器可接受3位二进制加权地址输入(A0,A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

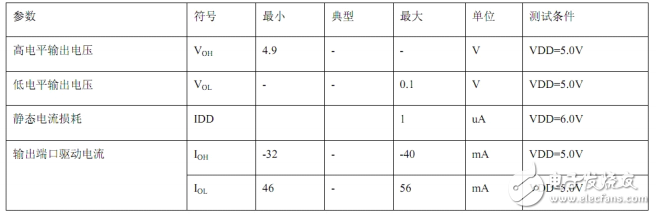

74hc138灌电流有多大

74HC138电流特性

74HC138的输入阻抗很大,在输入端不可能灌进超出datasheet上的电流,如果是输出端,灌进超出datasheet上的电流时,74HC138无法保证有效的逻辑电平输出。

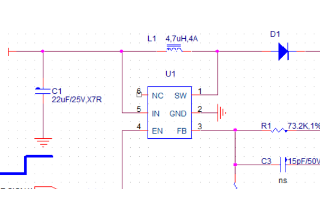

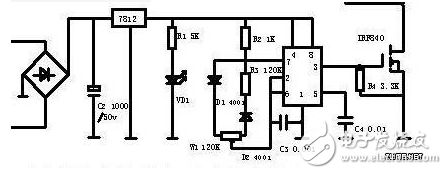

基于74hc138的4个输入8个输出的逻辑电路图设计

逻辑电路图

74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC138与74HC238逻辑功能一致,只不过74HC138为反相输出。

74HC138也就是38译码器,就是把3种输入状态翻译成8种输出状态.74HC138一共有1~6一共是6个输入引脚,但是其中4、5、6这三个引脚是使能引脚。使能引脚和我们前边讲74HC245的OE引脚是一样的,这三个引脚如果不符合规定的输入要求,Y0到Y7不管你输入的1、2、3引脚是什么电平状态,总是高电平。所以我们要想这个74HC138正常工作,ENLED那个输入位置必须输入低电平,ADDR3位置必须输入高电平,这两个位置都是使能控制端口。不知道大家是否记得我们第二课的程序有这么两句ENLED = 0;ADDR3 = 1;就是控制使这个74HC138使能的。

结语

关于74HC138的相关介绍就到这了,希望通过本文能让你对74HC138有更深的了解。

关于74hc138,电路图就介绍完了,您有什么想法可以联系小编。