今天小编要和大家分享的是74ls163,计数器相关信息,接下来我将从74ls163实现任意进制计数器,例4:使用74ls163构成一个计数状态 为二进制0111~1111的计数器.这几个方面来介绍。

例4:使用74ls163构成一个计数状态 为二进制0111~1111的计数器.

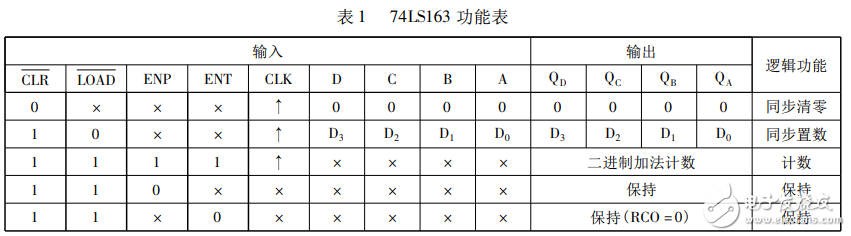

1、74LS163的功能及同步置数法

74LS163是集成4位二进制加法计数器,功能表如表1所示。其中CLK为时钟脉冲输入端、ENP及ENT为计数控制端、LOAD为同步预置数控制端、CLR为同步清零控制端、DCBA为预置数输入端、QDQCQBQA为状态输出端、RCO为进位输出端,芯片74IS163有从0000—111l共16个计数状态。

采用74LS163的同步预置数控制端或同步清零端构成进制计数器,方法是让计数循环过程跳过SN以及后面的各个状态,直接从SN-1状态转到全0状态。基本方法有清零法和置数法。

用同步置数法将74LS163构成N进制计数器,使用计数和同步置数功能时,需要在状态SN-1时给计数器的同步置数端发一个有效脉冲,使计数器在下一个计数脉冲到来时转到全0状态而非SN状态。同时,按自然态序进行计数的N进制计数器的预置数端必须设置为零,按逆排序计数的N进制计数器和按任意排序计数的N进制计数器的预置数端必须设置为计数状态中的最小数。

设计按自然态序进行计数的N进制计数器的步骤:

(1)写出N进制状态SN-1的二进制代码。

(2)写出SN-1状态的译码PN-1。因为利用同步置数法构成的N进制加法计数器时,状态SN—S2n-1不会出现,对应的最小项可作为随意项处理,利用这些随意项化简后,状态SN-1中代码为0的各个触发器的输出Q可被消去,所以译码时只要将SN-1状态中代码为1的各个触发器的输出Q相乘即可。

(3)写出置数逻辑表达式,即LD=PN-1。(4)74LS163其他输入端的设置,ENP=ENT=1,CR=1,DCBA=0000。

2、利用74LS163同步置数法构成N进制计数器的不同方法

2.1、按自然态序计数的N进制计数器(取前N个状态)

前面所介绍的构成N进制的方法,都是按自然态序计数的N进制计数器的设计方法。此处不再重述。

2.2、按逆排序计数的N进制计数器(取后N个状态)

当取后N个状态来构成N进制计数器时,因为需要计的最大数与所用计数器的最大计数相同,所以可用进位输出信号RCO来控制置数控制端LOAD,这样当计数器输出最大数并产生进位信号后,置数控制端LOAD=0,在下一个CP脉冲到来时,计数器将执行置数功能,即通过数据输入端DCBA置入需要计的最小数,于是在CP脉冲作用下,计数器又从最小数开始重新计数。

2.3、按任意排序计数的进制计数器(取中间N个状态)

当取中间N个状态来构成N进制计数器,可利用与非门检测需要计的最大数。当最大数出现时,与非门输出低电平,使置数控制端LOAD=0,在下一个CP脉冲到来时,计数器将执行置数功能,即通过数据输入端DCBA置入需要计的最小数,于是在CP脉冲作用下,计数器又从最小数开始重新计数。

3、同步置位法Multisim仿真设计

用 Multisiml0 版本构成 9 进制计数器为例,说明 Multisim 仿真设计。

3.1、按自然态序计数的9进制计数器仿真设计

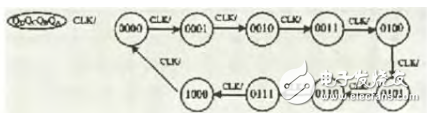

(1)按自然态序计数的9进制计数器状态图

同步置位法构成9进制计数器的状态图如图1所示,其中0000—1000共9个状态为正常的计数状态,作用9个时钟脉冲完成一个计数周期的循环。

图1自然态序计数9进制计数器状态图

(2)按自然态序计数的9进制计数器设计步骤

1)确定SN-1的二进制代码为:SN-1=S9-1=S8=1000

2)确定SN-1状态的译码PN-1为:PN-1=P9-1=P8=QD

3)写出置数逻辑表达式,即LD=PN-1=QD

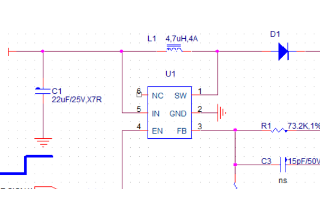

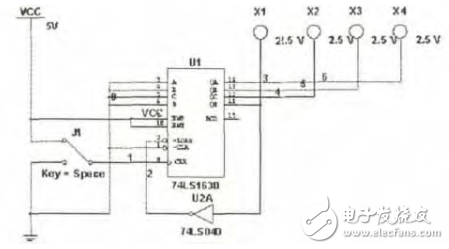

4)构建仿真电路

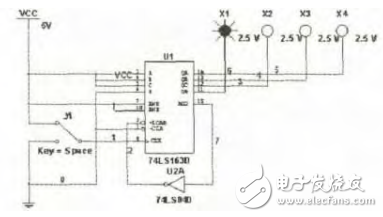

构建的仿真电路如图2所示。其中脉冲信号选择由双向开关构成的手动脉冲信号,以便实验中更好地观察每个时钟作用后计数器的状态变化情况。在Multisim中,集成4位二进制计数器74LS163的时钟脉冲触发方式为CLK为下降沿触发与实际器件不附(实际器件为上升沿触发方式),仿真实验时应进行说明。显示器件使用不同颜色的探针,更加直观地显示了实验效果。

图2自然态序计数9进制计数器仿真电路

(3)仿真结果分析在图2中,探针X1、X2、X3、X4分别显示输出端QD、QC、QB、QA电平,当输出为1(高电平)时探针发光,为0(低电平)时探针不发光。

当第一个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=0001;当第二个CLK脉冲信号下降沿到来后计数器状态为QDQCQBQA=0010;当第三个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=0011;当第四个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=0100;当第五个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=0101;当第六个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=0110;当第七个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=0111;当第八个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=1000,此时,LOAD=0但并没有进行同步置位;当第九个脉冲信号CLK下降沿到来时,进行同步置数,将数据输入端DCBA=0000送入计数器,使计数器状态为QDQCQBQA=0000。经过9个时钟脉冲信号作用后完成一个计数周期的循环,仿真实验结果和图1所示状态图的要求一致。

3.2、按逆排序计数的9进制计数器(取后9个状态)

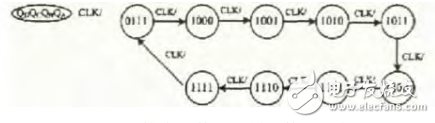

(1)按逆排序计数的9进制计数器的状态图

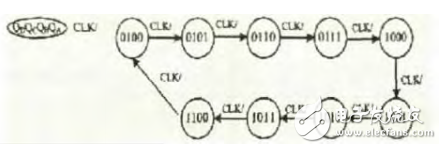

同步置位法构成9进制计数器的状态图如图3所示,其中0111—1111共9个状态为正常的计数状态,作用9个时钟脉冲完成一个计数周期的循环。

图3按逆排序计数9进制计数器状态图

(2)按逆排序计数的9进制计数器设计步骤

当取后9个状态来构成9进制计数器时,因为需要计的最大数与所用计数器的最大计数相同,因此可确定SN-1状态中最小状态的最小数的数据输入端的输入数据为:DCBA=0111,置数逻辑表达式为LD=RCO。

(3)构建仿真电路

构建的仿真电路如图4所示。

图4按逆排序计数9进制计数器仿真电路

(4)仿真结果分析

在图4中,探针X1、X2、X3、X4分别显示输出端QD、QC、QB、QA电平,当输出为1(高电平)时探针发光,为0(低电平)时探针不发光。

当第一个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=1000;当第二个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=1001;当第八个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=1111,此时进位端RCO=1产生进位,LOAD=RCO=0,但并没有进行同步置位;当第九个脉冲信号CLK下降沿到来时,进行同步置数,将数据输入端DCBA=0111送入计数器,使计数器状态为QDQCQBQA=0111。经过9个时钟脉冲信号作用后完成一个计数周期的循环,仿真实验结果和图3所示状态图的要求一致。

3.3、按任意排序计数的9进制计数器(取中间9个状态)

(1)按任意排序计数的9进制计数器状态图

同步置位法构成9进制计数器的状态图如图5所示,其中0100—1100共9个状态为正常的计数状态,作用9个时钟脉冲完成一个计数周期的循环。

图5按任意排序计数9进制计数器状态图

(2)按任意排序计数的进制计数器设计步骤

当取中间9个状态来构成9进制计数器,可利用与非门检测需要计的最大数。当最大数出现时,与非门输出低电平,使置数控制端LOAD=0,即LOAD=QDQC。通过数据输入端DCBA置入需要计的最小数,即DCBA=0100。

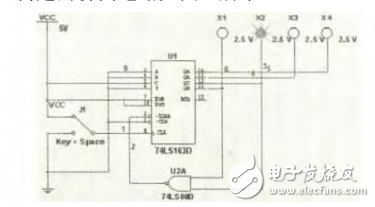

(3)构建仿真电路

构建的仿真电路如图6所示。

图6按任意排序计数9进制计数器仿真电路

(4)仿真结果分析

在图6中,探针X1、X2、X3、X4分别显示输出端QD、QC、QB、QA电平,当输出为1(高电平)时探针发光,为0(低电平)时探针不发光。

当第一个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=0101;当第二个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=0110;当第八个脉冲信号CLK下降沿到来后计数器状态为QDQCQBQA=1100,此时LOAD=QDQC=0,但并没有进行同步置位;当第九个脉冲信号CLK下降沿到来时,进行同步置数,将数据输入端DCBA=0100送入计数器,使计数器状态为QDQCQBQA=0100。经过9个时钟脉冲信号作用后完成一个计数周期的循环,仿真实验结果和图5所示状态图的要求一致。

关于74ls163,计数器就介绍完了,您有什么想法可以联系小编。