今天小编要和大家分享的是74ls138,译码器相关信息,接下来我将从74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路),sn74ls138n hd74ls138p 逻辑多路复用/解码器芯片 直插dip16这几个方面来介绍。

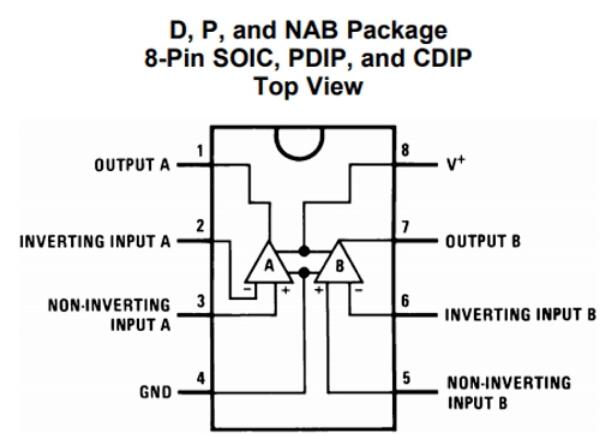

sn74ls138n hd74ls138p 逻辑多路复用/解码器芯片 直插dip16

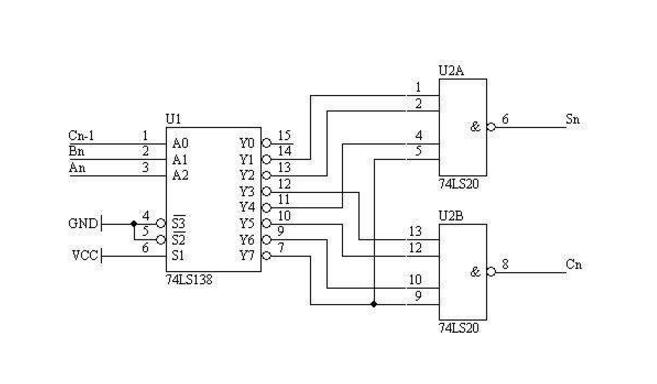

74ls138应用电路一:全加器电路

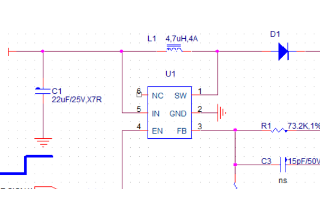

全加器有3个输入端:a,b,ci;有2个输出端:s,co.与3-8译码器比较,3-8译码器有3个数据输入端:A,B,C;3个使能端;8个输出端,OUT(0-7)。这里可以把3-8译码器的3个数据输入端当做全加器的3个输入端,即3-8译码器的输入A、B、C分别对应全加器的输入a,b,ci;将3-8译码器的3个使能端都置为有效电平,保持正常工作;这里关键的就是处理3-8译码的8个输出端与全加器的2个输出的关系。

将3-8译码器的输出OUT(1、2、4、7)作为一个4输入的或门的输入,或门的输出作为加法器的和;将3-8译码器的输出OUT(3、5、6、7)作为一个4输入的或门的输入,或门的输出作为加法器的进位输出。当加法器的输入分别为:a=1,b=0,ci=1时,对应3-8译码器的输入为A=1,B=0,C=1,这是译码器对应的输出为OUT(5)=1,其余的为0,根据上面设计的连接关系,s=0,co=1,满足全加器的功能。

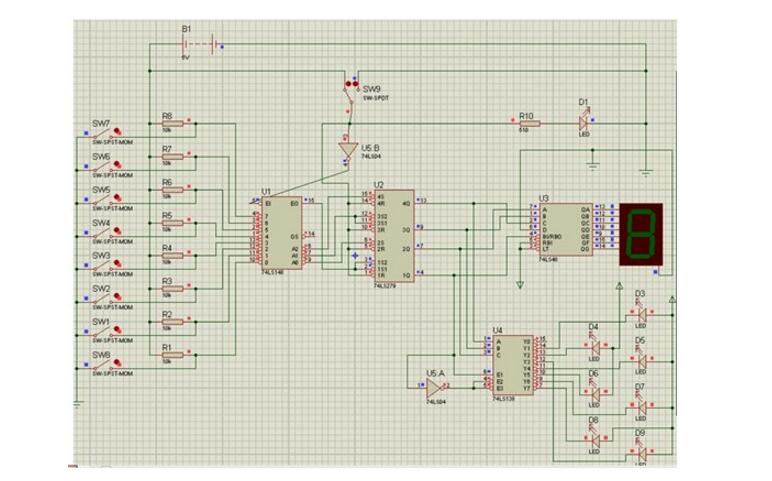

74ls138应用电路二:抢答器电路

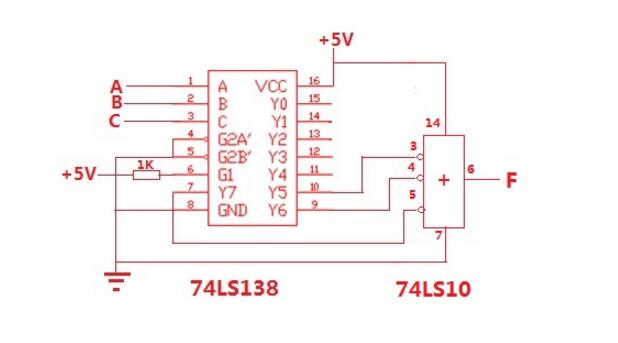

74ls138应用电路三:实现逻辑函数

F = ABC + A‘BC + AB’C

= 111 + 110 + 101

= Y7 + Y6 + Y5

按照74LS138的规则,A 是低位(LSB),D 是高位(MSB)。

74ls138 译码输出是低电平有效,用 74LS10 与非门,实际逻辑是输入低电平有效的或门。

74ls138应用电路四:全减器电路

74LS138实现全减器电路图

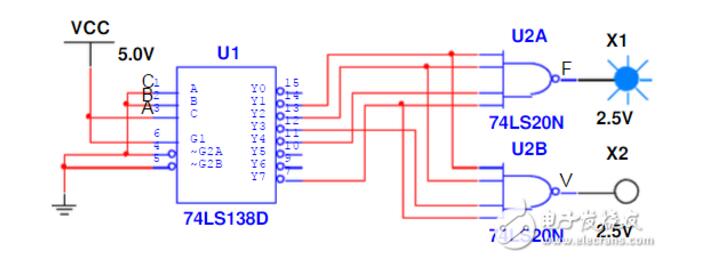

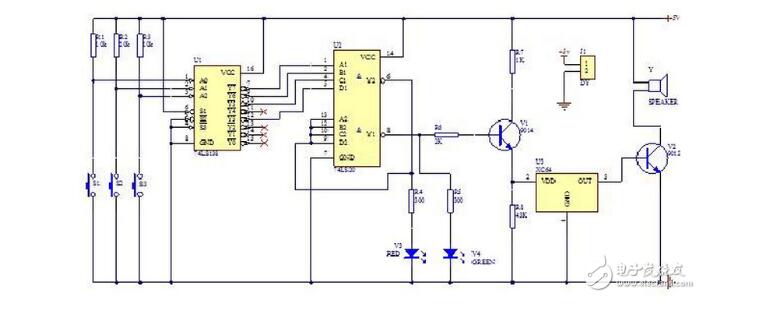

74ls138应用电路五:三人表决器电路

三人表决器主要由一个3-8位译码器(74LS138)和2个4输入与非门(74LS20)组成。通过三个按钮接受用户输入。按钮按下表示同意,不按下表是否决,当没有人按下按钮时,或只有一个人按下按钮时,例如,S1按下,而S2和S0未按下,则红灯亮,绿灯灭,蜂鸣器无声音,表示否决,当有两个人及以上的人按下按钮后,例如,S1和S2按下,则红灯灭,绿灯亮,蜂鸣器发音,表示通过。运用74LS138译码器和四输入与非门74LS20实现该逻辑功能。

关于74ls138,译码器就介绍完了,您有什么想法可以联系小编。