今天小编要和大家分享的是ad9850相关信息,接下来我将从ad9850应用电路图大全(信号发生器/与单片机接口电路),共111 件ad9850模块相关商品这几个方面来介绍。

共111 件ad9850模块相关商品

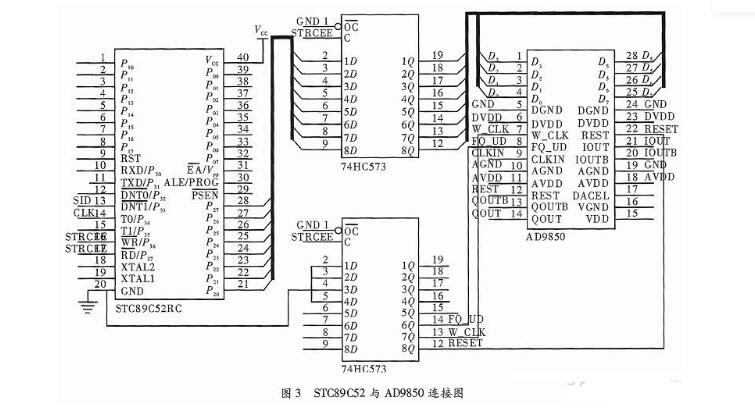

ad9850应用电路一:

AD9850的40位频率/相位控制字可通过并行或串行两种方式送入器件。选用并行传输方式,充分发挥芯片AD9850的高速性能。在并行方式下连续输入 5次数据,每次输入8位(1 Byte),将40位频率/相位控制字送入器件。系统中,单片机通过数据锁存器和控制锁存器来实现对AD9850模块的控制,数据锁存器打开时,控制锁存器关闭,此时传输数据;控制锁存器打开时,数据锁存器关闭,此时根据AD9850的时序对W_CLK、FQ_UD、RESET执行相应的操作。单片机 89C52控制AD9850工作连线图,如图3所示。

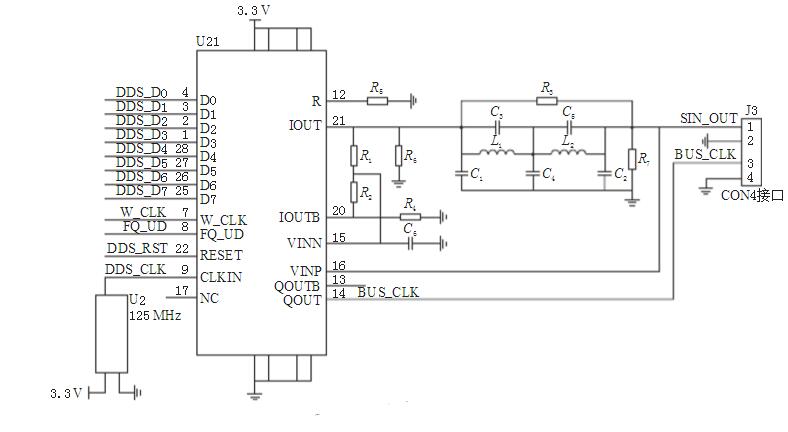

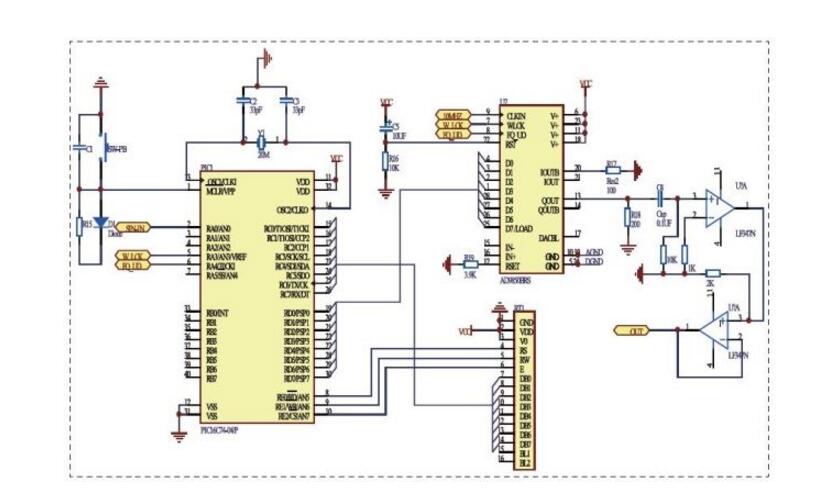

ad9850应用电路二:

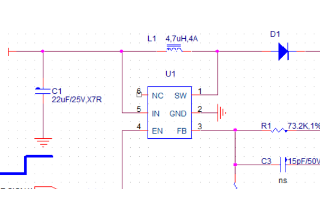

总线方式并行接口占用的单片机资源较少,而且本设计中信号发生器只是作为单片机控制模块的外围扩展模块之一,因此AD9850工作在控制字并行输入方式。此时,AD9850仅作为一扩展芯片只占用一个地址。其原理图如图4所示。

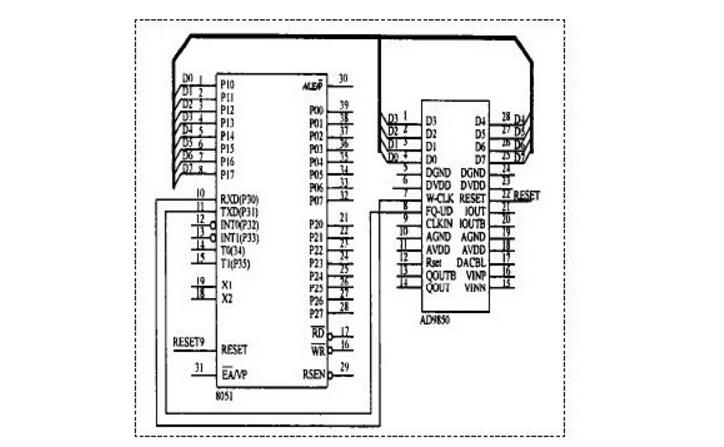

ad9850应用电路三:

AD9850与单片机接口电路,需要考虑以下几点:

①AD9850控制字写入方式选择.AD9850控制字的写入方式有串行和并行两种。并行写入方式的优点是数据传输的速度快,能够提升整个系统的处理速度,为了充分发挥芯片的高速性能,应在单片机资源允许的情况下尽可能选择并行方式,所以,本系统采用8051单片机作为控制核心,通过并行写入控制字的方式控制AD9850芯片。如图4所示,AD9850的数据线D0~D7与P1口相连。

AD9850与单片机接口电路

②FQUD和WCLK与单片机连接.AD9850的FQUD控制信号和WCLK控制信号与分别与8051单片机的P3.0(10引脚)和P3.1(11引脚)相连,所有的时序关系均可通过软件控制实现。

③RESET与单片机连接.AD9850的晶体振荡器采用100MHz,AD9850的复位(RESET)信号为高电平有效,且脉冲宽度不小于5个参考时钟周期。由于单片机采用12MHz晶振时,它的高电平时间能够满足AD9850复位要求,故可将AD9850的复位端与单片机的复位端直接相连.

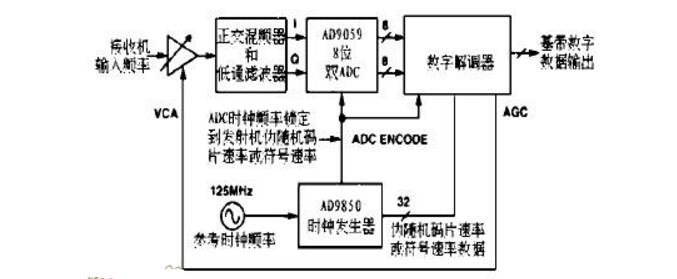

ad9850应用电路四:

AD9850 时钟发生器在扩频接收器中的应用

ad9850应用电路五:

AD9850是美国AD公司生产的高集成度的DDS合成芯片。它采用32位相位累加器,截断成14位,输入正弦查询表,查询表输出截断成10位,输入到DAC。DAC输出两个互补的模拟电流,接到滤波器上。但是AD9850直接产生的信号幅度只有2V左右,而且是单极性的。而测试的时候需要的是双极性的正弦信号,因此DDS输出的信号还要经过隔直和放大。AD9850输出的信号经过RC高通滤波器,将直流分量滤除,输出交流信号,再经放大器放大,电压跟随,输出幅度适当、带载能力较强的信号源。电路如图所示。

ad9850应用电路六:

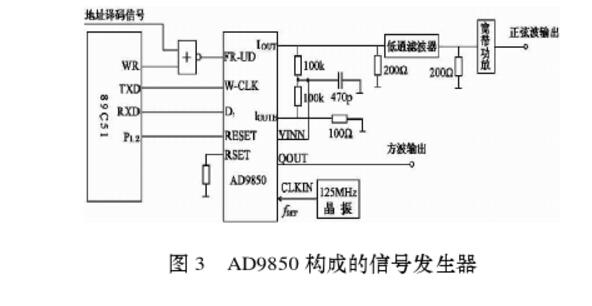

图3为AD9850和单片机89C51构成的数控信号发生器为了减少电路连线,AD9850与单片机之间采用串行连接方式,回参考时钟由125MHZ的晶体振荡器产生89C51串行口设置为方式0输出,TXD作为时钟信号与W-CLK相连,RXD作为数据信号与Dr相连,地址译码信号和WR经或非后与FR-UD相连,主复位RESET由单片机的P,2控制。程序编写时要注意:先发送40位频率相位控制字低位字节的低位,再发送高位字节,40位控制字分5个字节单元发送,每个字节是否发送完可通过查询串行口控制寄存器SCON中的TI位,5个单元的控制字发送完后,单片机通过执行一条写指令MOVX@DPTR,A就可以完成更新输出频率和相位。图3中DAC正输出端IOUT驱动2002、5极点低通滤波器,而滤波器后面又接一个2002负载,使等效负载为1002。DAC互补输出电流驱动1002负载。输出的正弦信号连到比较器的VINP端,DAC两个输出间的100K2分压输出被电容去耦后,用作内部比较器的参考电压。

关于ad9850就介绍完了,您有什么想法可以联系小编。