今天小编要和大家分享的是CD4518,数字钟电路相关信息,接下来我将从CD4518组成的数字钟电路(cd4518引脚图及功能表与工作原理),数显式四位高精度通用定时器(cd4040,cd4518,cd4029)电路图这几个方面来介绍。

数显式四位高精度通用定时器(cd4040,cd4518,cd4029)电路图

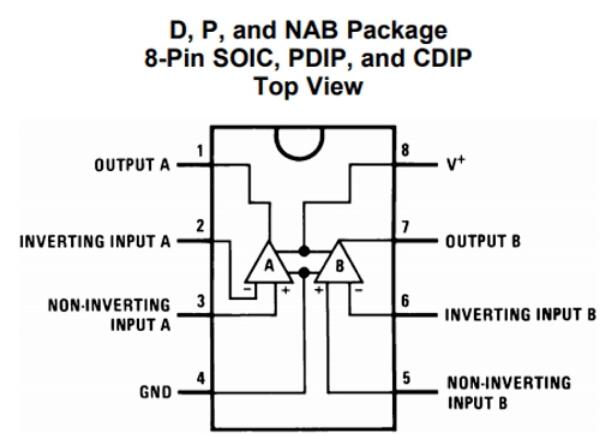

CD4518引脚图及功能描述

CD4518是一个双BCD同步加计数器,由两个相同的同步4级计数器组成。

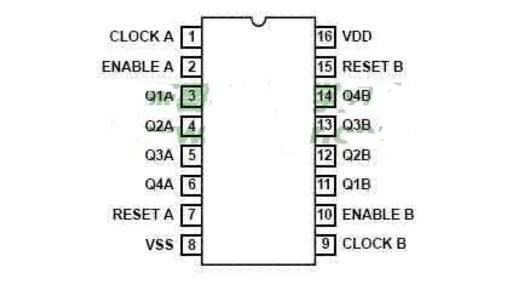

CD4518引脚图

CD4518引脚功能如下:

1CP、2CP:时钟输入端。

1CR、2CR:清除端。

1EN、2EN:计数允许控制端。

1Q0~1Q3:计数器输出端。

2Q0~2Q3:计数器输出端。

Vdd:正电源。

Vss:地。

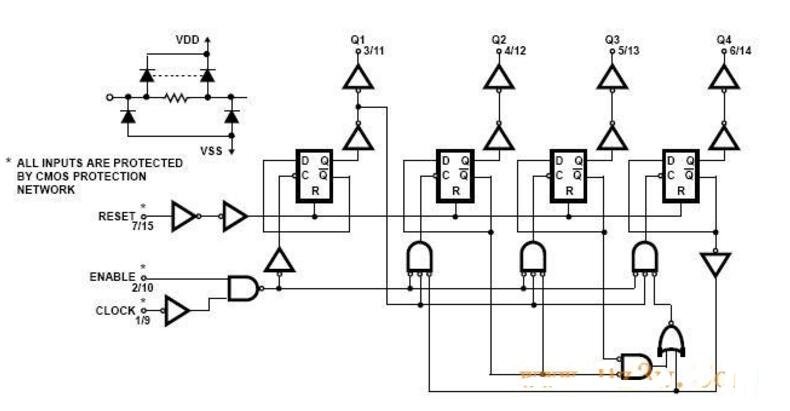

CD4518逻辑功能图

cd4518工作原理

CD4518/CC4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器,其功能表如真值表所示。每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。由表可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数。

CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数。CD4520/CC4520为二进制加计数器,由两个相同的内同步4级计数器构成。计数器级为D型触发器,具有内部可交换CP和EN线,用于在时钟上升沿或下降沿加计数。在单个单元运算中,EN输入保持高电平,且在CP上升沿进位。CR线为高电平时,计数器清零。计数器在脉动模式可级联,通过将Q3连接至下—计数器的EN输入端可实现级联,同时后者的CP输入保持低电平。

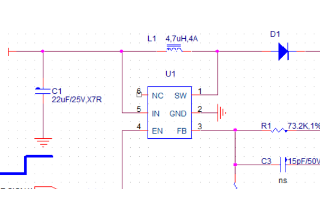

CD4518典型应用电路

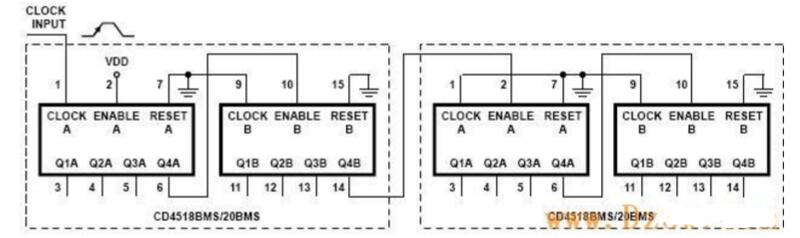

串联4个计数器上升沿边缘触发

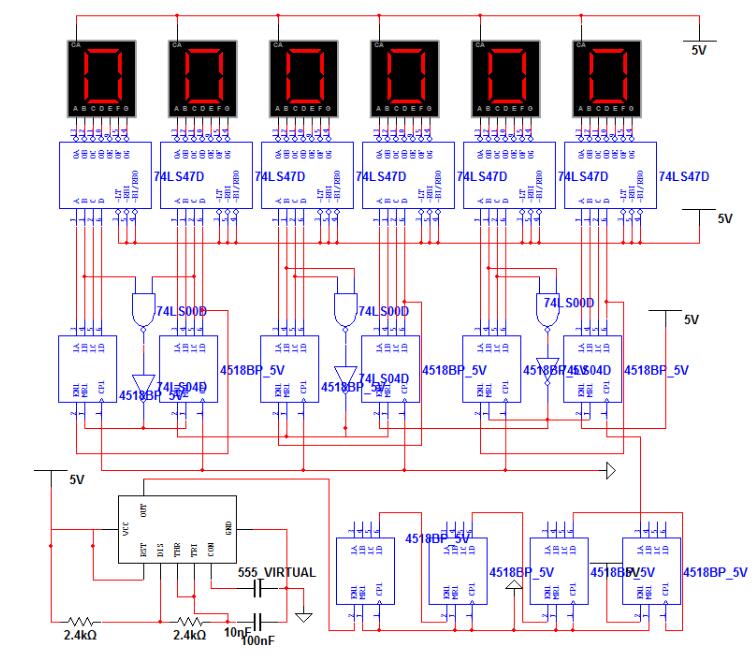

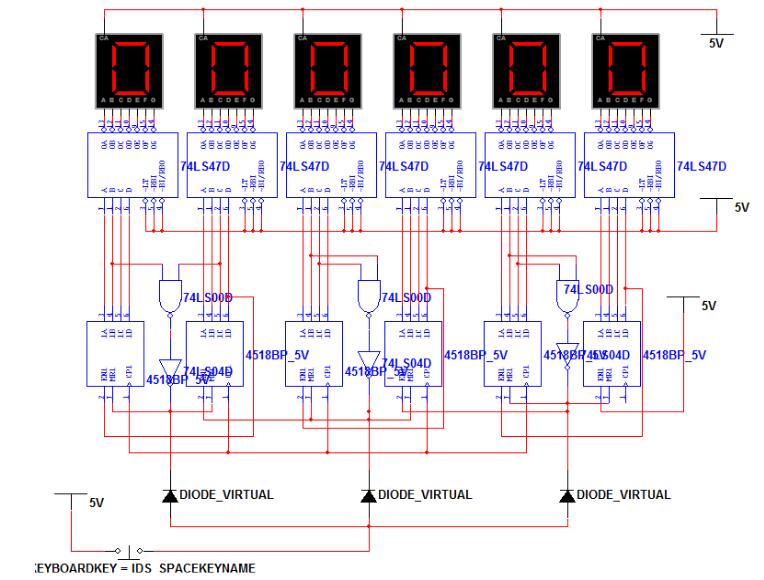

CD4518组成的数字钟电路

1、不能进行清零的数字钟

其脉冲式用NE555产生的一个2000Hz的脉冲,用CD4518进行四次分频,使其频率达到1Hz,用此频率对数字钟进行脉冲驱动。时、分、秒的计数用CD4518,分别用一片实现对时、分、秒的计数,在此需要用到还有74LS00和74LS04,用其进行复位。译码器电路采用74LS47对数码显示管进行驱动。

CD4518控制功能:CD4518有两个时钟输入端CP和EN,若用时钟上升沿触发,信号由CP输入,此时EN端为高电平(1),若用时钟下降沿触发,信号由EN输入,此时CP端为低吨平(0),同时复位端Cr也保持低电平(0),只有满足了这些条件时,电路才会处于计数状态。否则没办法工作。

2、能够清零的数字时钟

图中CD4518的清零端连接了三个二极管,二极管具有单向导通特性,使每个清零端之间没有影响,当清零端为高电位的时候进行清零,所以,按下清零开关,清零端为高电位,时、分、秒清零。

关于CD4518,数字钟电路就介绍完了,您有什么想法可以联系小编。