今天小编要和大家分享的是开关电容电路相关信息,接下来我将从关于开关电容电路设计的相关知识,开关电容电路中运算放大器输入端的共模电压调节电路这几个方面来介绍。

开关电容电路中运算放大器输入端的共模电压调节电路

本文将列举出了关于设计开关电容电路过程中的3种情况,一个是恒压源Vo给电容C充电的问题,第二个是电压为Vo的电容如何给一个电压为V1的电容充电问题等。本文将会进行详细的解说。

偶然点到这个问题,这是一个很有意思的现象,恰好我最近就在学习和设计开关电容电路(switched capacitor converter),愿意和大家探讨学习一下。

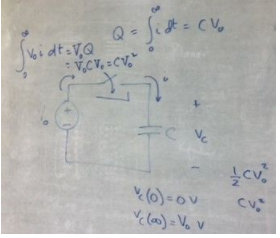

首先我们看第一种情况:一个恒压源Vo给电容C充电

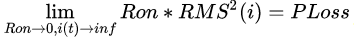

可以看到电压源损失的能量是CVo^2, 而电容C上获得的能量是0.5CVo^2,那么一半的能量在充电过程中损失了。如果我们假设开关是理想的,Ron=0,那么loss是那里产生的呢?有答案认为是电磁辐射发散出去的。我们知道,如果开关是理想的,在接通开关的一瞬间,开关上流过的电流是无穷大的,一个无穷大的电流流过Ron=0的开关,产生的loss其实是一个取极限的结果: 。不管怎样,我们知道了一个恒压源Vo给电容C充电要有0.5CVo^2的loss.

。不管怎样,我们知道了一个恒压源Vo给电容C充电要有0.5CVo^2的loss.

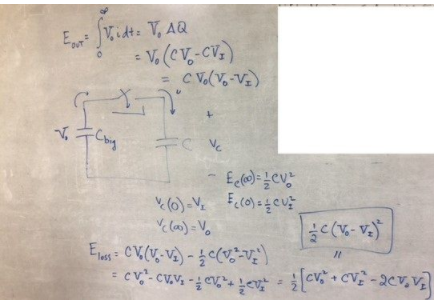

第二种情况:一个电压为Vo的电容给一个电压为V1的电容充电(Vo》V1),两者电容值都是C,我们仍然假设开关是理想的,Ron=0.

可以看到V0电容损失的能量是CVo(Vo-V1), 而V1电容上获得的能量是0.5C(Vo^2-V1^2),充电过程中损失的loss是0.5*C(V0-V1)^2,所以,我们可以看到电压不同的电容之间充电也会有loss的。

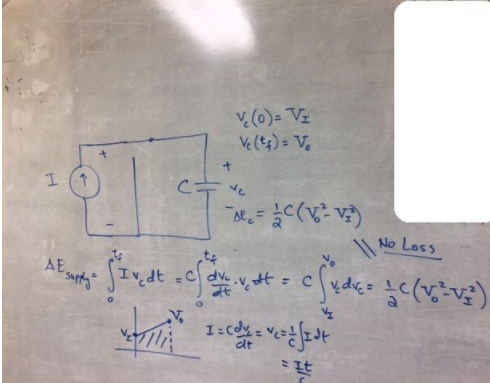

那么有些不死心的朋友要问了:有没有情况下给电容充电是无损(lossless)的呢?答案是有的,我们来看第三种情况:一个电流源I给电容充电,把电容的电压从V1提升到V0.

可以看到电流源I损失的能量等于电容上得到的能量等于0.5C(Vo^2-V1^2),充电过程是无损的!

以上就是开关电容电路(switched capacitor converter)的loss雏形,那么我们为什么要费尽心思搞这个有loss的switched capacitor converter呢?这是因为在实际生活中,好电容易得,但好电感难求!尤其是在集成电路(integrated circuit)领域,magnetics(比如电感、变压器)是很难集成到芯片里面的,如果我们只用电容和transistor搭建一个converter,功率密度(power density)会极大提高!1k-2k W/inch³ 的converter也是有可能做出来的!

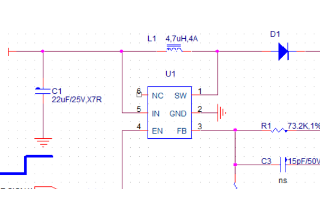

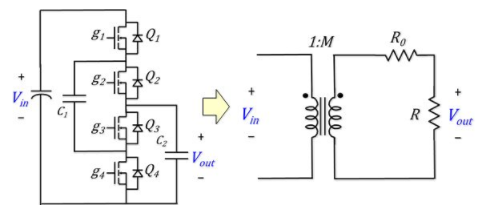

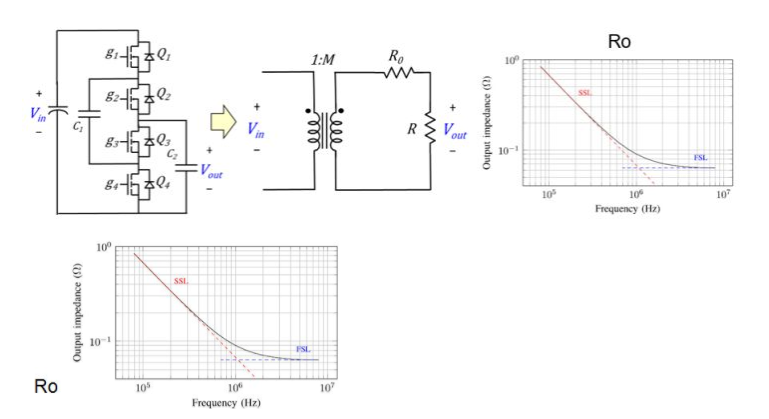

举一个例子,我们来看一个最经典结构: 2-1 ladder switched capacitor converter。其中gate signal:Q1与Q3同时开启与关闭,Q2与Q4同时开启与关闭。g1与g2,g3与g3是half bridge,也就是两对complementary开关的管子。Marek和Dragan在1995年一篇TPE [1] 上提出任何switched capacitor converter都可以建模成一个DC变压器和一个输出电阻Ro,DC变压器的变压比M代表了converter的conversion ratio,输出电阻Ro代表了Converter的Loss。这里存在一个所谓的“Fast Switching Limit”和“Slow Switching Limit”问题了。这是什么意思呢?就是说SC converter在不同频率下代表Loss的Ro是不同的!那么如何求出M和RFSL(Fast Switching Limit Rout)和RSSL(slow Switching Limit Rout)成了我们关心的问题。

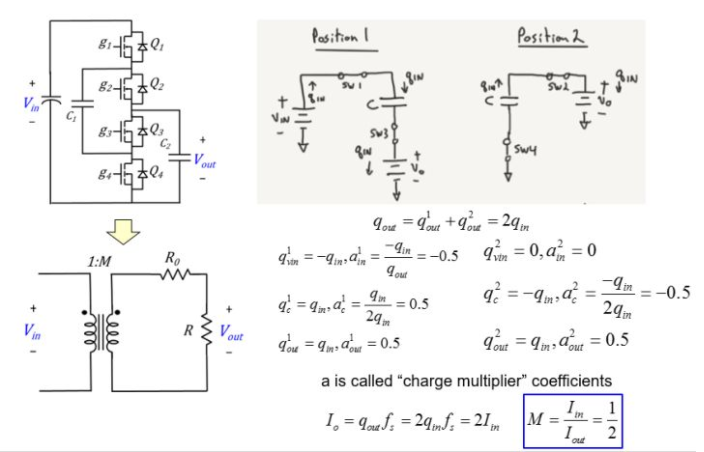

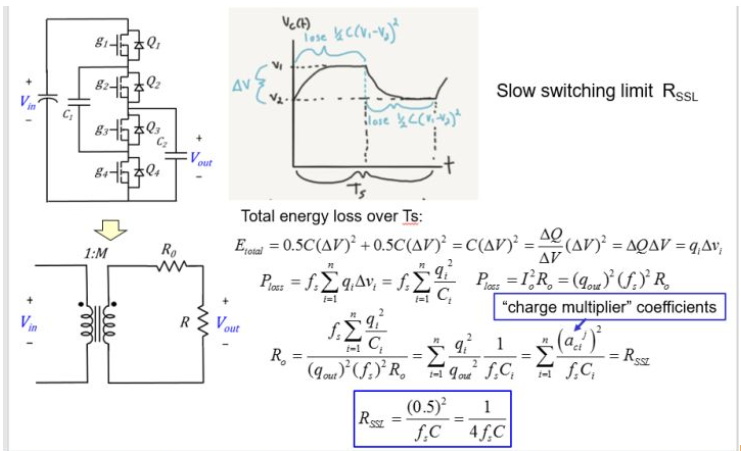

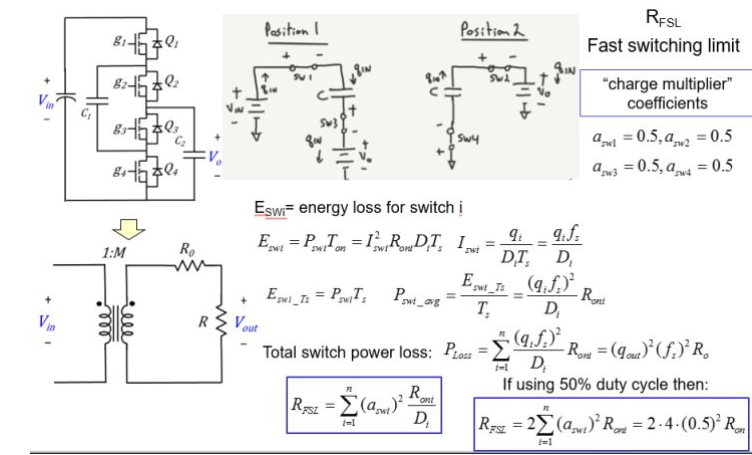

Mike.Seeman大神在他MS thesis [2] 里面详细阐述了这个问题,他用的是charge flow analysis,意思就是求出每个情况下通过各个elements的charge,然后进行M和loss Ro的计算。具体细节我就不赘述了,我自己瞎逼推导了一下,大家随便看看。

Conversion Ratio M:

Slow Switching Limit:

Fast Switching Limit:

最终,我们把Switched Capacitor Converter进行了简单的建模:

值得注意的是,Loss Ro的计算只考虑的conduction loss,而且是用平均电流代替了RMS电流来计算loss,没有考虑switching loss和gating loss,所以这只是一个很粗糙的模型,只是让我们直观感受一下converter loss与开关频率frequency的关系。我们其实希望SC converter工作在FSL范围内,这样的loss比SSL内小,但是我们又不希望频率过高,这样会带来其他switching loss和gating loss的损失。

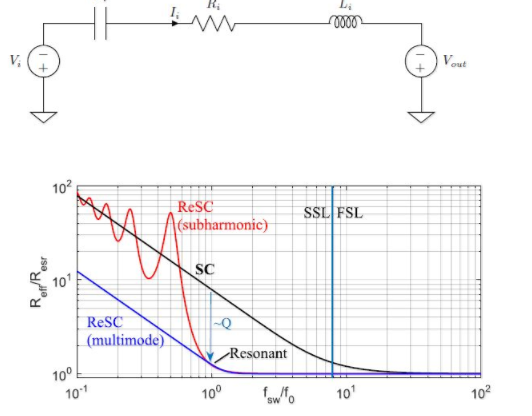

SC Converter的好处例如high power density,利于集成等优点说了很多,但是缺点也是不容忽视的:比如conversion ratio固定,不能regulate output voltage;transient current很大。那么我们有没有办法解决这个问题呢?答案是有的,解决的手段就是用hybrid/resonant switched capacitor converter(还记得在第三幅图中电流源I给电容充电是无损的那个例子吗?)。在topology方面,我们在SC converter的输出或输入端串联一个传统的buck或者boost converter,或者在tank里面引入resonant电感,来实现soft charge和regulation。在control方面我们可以有frequency and/or phase shift control。具体细节这里就不再赘述了。

PS. 比起前面花里胡哨的charge flow analysis来分析Loss,Sarah和Jason Stauth大神在COMPEL 2016上提出了switched capacitor和 Hybrid/Resonant Switched-Capacitor Converters的Ro的通式 Ro(fs) ,对 Ro(fs)取fs-》0和fs-》inf 两端极限就可以得到“Fast Switching Limit”和“Slow Switching Limit”的Ro了。可谓重剑无锋,大巧不工,这篇文章获得了2016 COMPEL最佳文章之一。

关于开关电容电路就介绍完了,您有什么想法可以联系小编。