今天小编要和大家分享的是74ls290,电子时钟相关信息,接下来我将从74ls290实现电子时钟电路设计方案详解,电路 电路图 电子 原理图 1487_762这几个方面来介绍。

电路 电路图 电子 原理图 1487_762

电子钟亦称数显钟(数字显示钟),是一种用数字电路技术实现时、分、秒计时的装置,与机械时钟相比,直观性为其主要显著特点,且因非机械驱动,具有更长的使用寿命,相较石英钟的石英机芯驱动,更具准确性。电子钟已成为人们日常生活中必不可少的必需品,广泛用于个人家庭以及车站、码头、剧院、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大地方便。

相对于其他时钟类型,它的特点可归结为“两强一弱”:比机械钟强在观时显著,比石英钟强在走时准确,但是它的弱点为显时较为单调。电子钟更为方便快捷,实用。本文介绍74ls290实现电子时钟电路的设计方案详解。

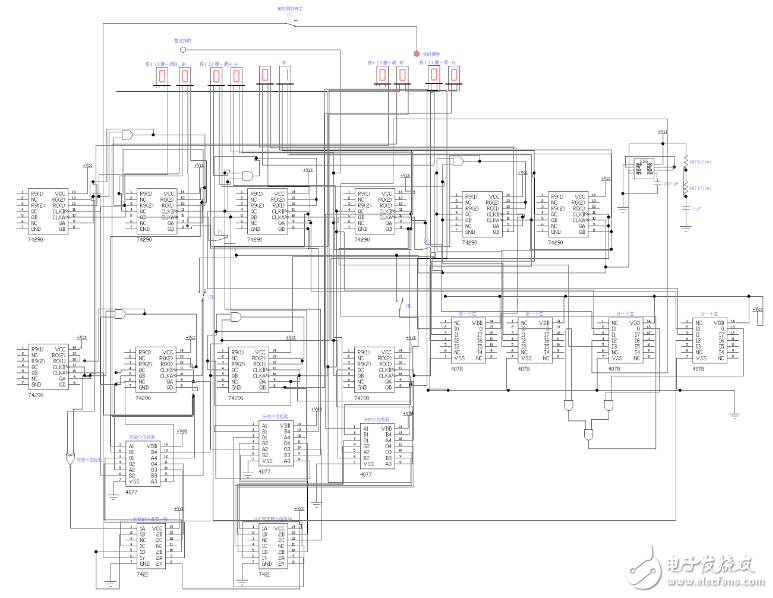

总电路图设计思路

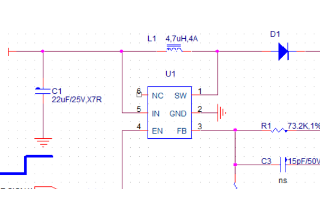

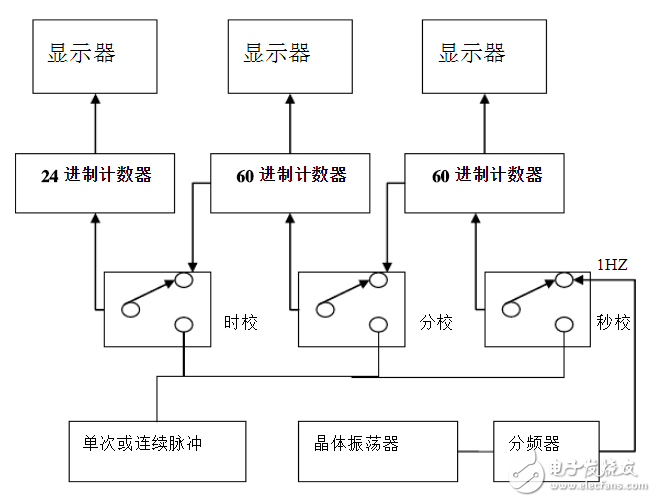

多功能数字钟是一个对标准频率(1HZ)进行计数的计数电路。它由振荡器、分配器、计数器、译码器和显示电路组成。振荡器与分配器组成秒脉冲输出装置,秒脉冲信号输入计数器进行计数,并把累计结果以“时”、“分”、“秒”的数字显示出来。秒计数器电路计满60后触发分计数器电路,分计数器计满60后触发时计数器点路,当计满24小时候又开始下一轮的循环计时。

通过校时电路可以对分和时进行校时。且计时过程具有报时功能,当时间到达整点前5秒蜂鸣器每秒响1次,当到达整点时再响高音一次。

闹钟电路通过设置目标时间,与计时电路进行比较,相同则输出电信号发出报警。

系统设计框图

单元电路设计

1、递增计数器

(1)递增计数器的设计

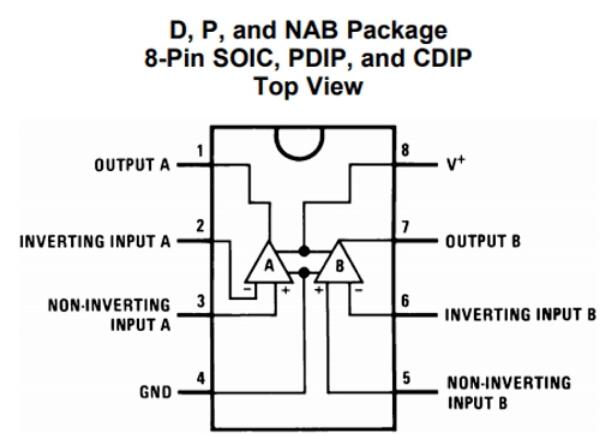

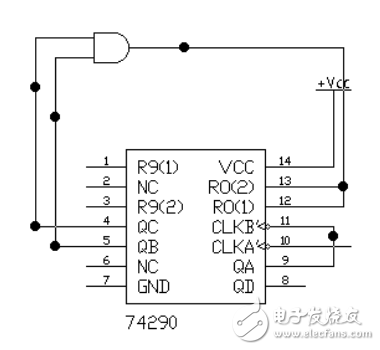

这一部分电路采用中规模集成电路74ls290实现加法的计数,由课题得知需要60进制以及24进制计数器。由74290功能得知,将CP0和Q3相连,计数脉冲由CP1输入得到8421BCD码十进制计数功能。

如要得到60进制加数器,需要将一个74290接成7进制组成十位,一个74290接成10进制组成个位并且将个位的Q3端接到十位的CP0。下图为6进制接法

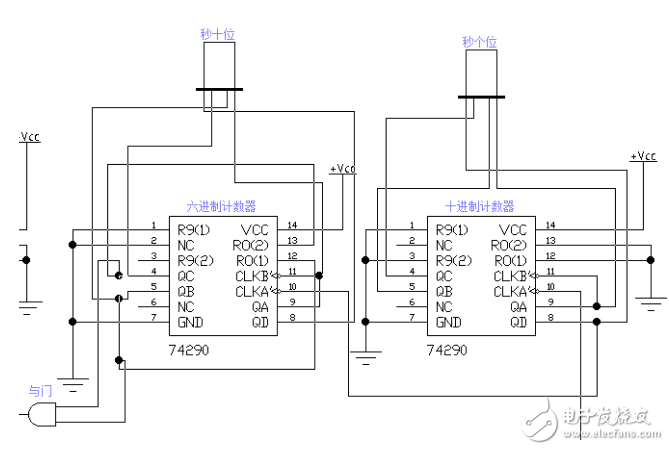

(2)60进制递增计数器的电路图

加法计数器

2、秒、分、时计时器

这一部分电路采用中规模集成电路74ls290组成的加数器实现秒、分、时的计数,其中秒、分、时为六十进制,时为二十四进制。从图二可以看出秒、分两组六十进制计数电路完全相同。当计数到59时,再来一个脉冲变成00,然后再重新开始计数。利用异步清零反馈到CR端而实现个位十进制,十位六进制的功能。

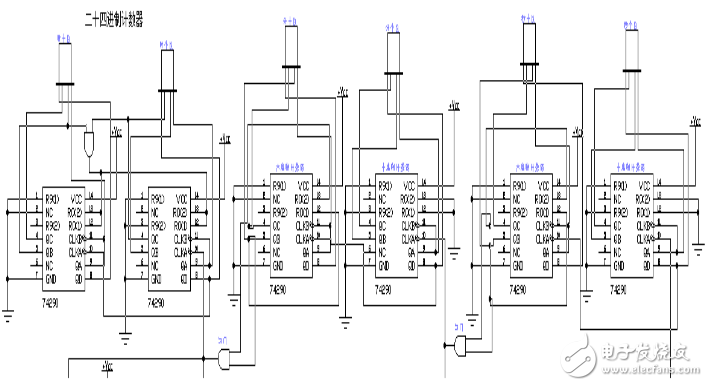

时计数器分为二十四进制,当开始计数时,各位按十进制计数,当计到23时,这时再来一个脉冲,应该回到0。所以这里必须使个位既能完成十进制计数,又能在高低位满足23这一数字后,时计数器清0,图中使用了十位的2和个位的4相与非后再清0。其电路图如下所示

秒、分、时计数器

3.闹钟系统及其显示

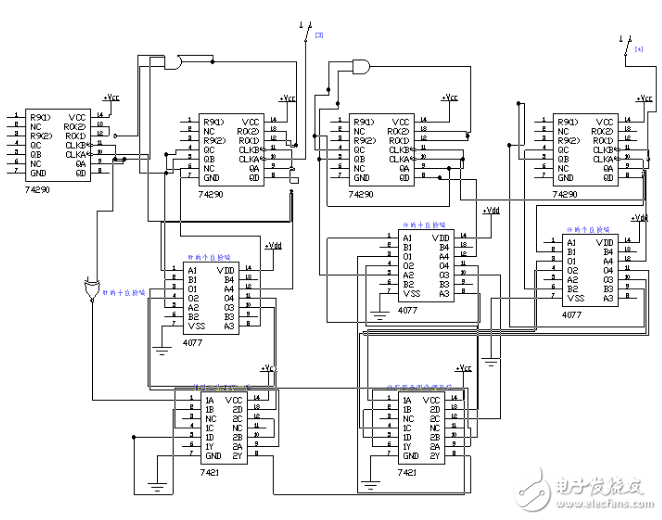

闹钟由可调时、分显示器,4个74290芯片,3个4077芯片和两个7421芯片的电路构出时钟的多功能部分。其中,四个74290和四个显示器构成定时闹钟的显示部分(调时部分可以由开关3、4直接控制电路与振荡器的连接来实现);4077芯片的作用是比较实际时钟部分与闹钟部分的输出数据是否一致,再由两个7421芯片校验作最后校验,当全部输出对比为真时,则发光二极管亮起来,实现定时闹钟功能

其电路图如下所示:

闹钟电路图

4.调时、调分电路

如电路图(全图),将时、分电路的计数器直接接到振荡器,再分别由开关“1”及“2”控制电路的接通与断开,实现调时、调分。

总电路图

总电路图设计如图所示

关于74ls290,电子时钟就介绍完了,您有什么想法可以联系小编。