今天小编要和大家分享的是74ls160,计数器相关信息,接下来我将从74ls160构成24进制计数器,2个74ls192和一个74ls00怎么构成24进制计数器(有原理这几个方面来介绍。

2个74ls192和一个74ls00怎么构成24进制计数器(有原理

24进制计数器电路(一)

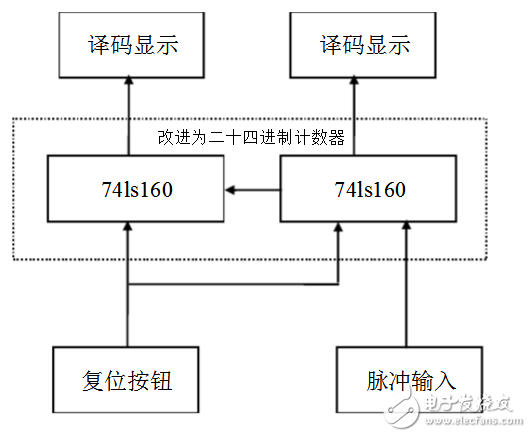

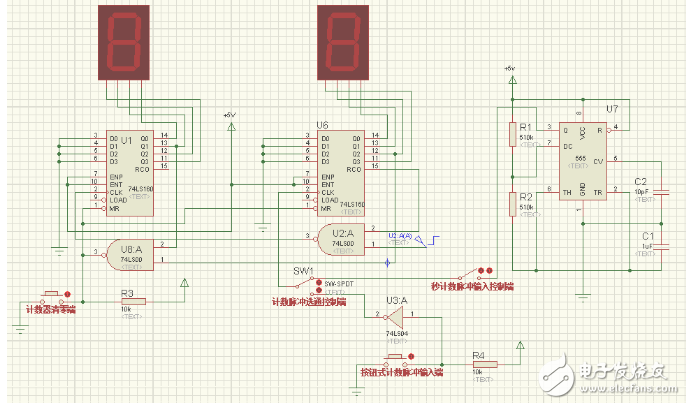

1、计数器设计框图

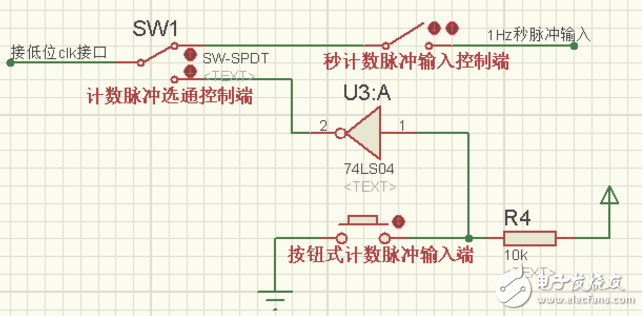

通过单刀双掷开关选择计数脉冲选择计数脉冲,其中,按钮式计数脉冲输入端,每按下一次,计数加一。

2、秒计数脉冲

555定时器是一种模拟电路和数字电路相结合的中规模集成器件,它性能优良,适用范围很广,外部加接少量的阻容元件可以很方便地组成单稳态触发器和多谐振荡器,以及不需外接元件就可组成施密特触发器。该电路有一个秒脉冲控制端,用于开启及停止脉冲输入。

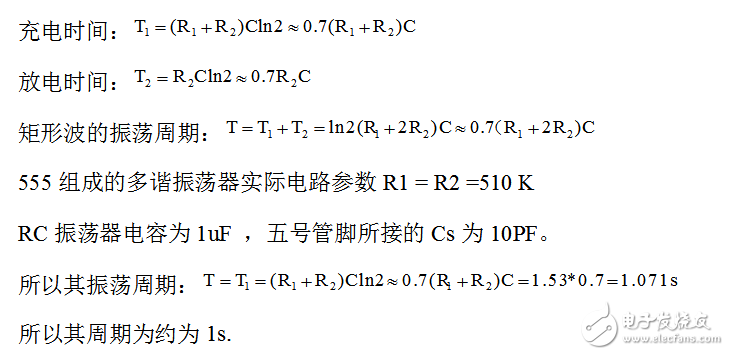

由多谐振荡器原理,结合上图可知其振荡周期T=T1+T2。T1为电容充电时间,T2为电容放电时间。

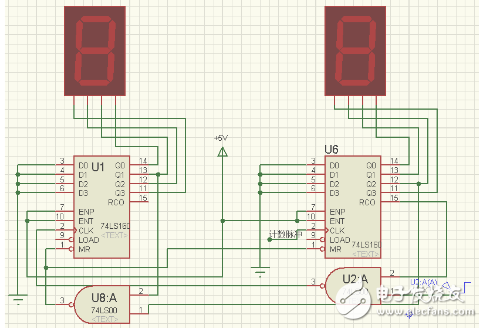

3、二十四进制计数器

利用74ls160把高位和低位端的脉冲通过一个与非门同时送入高位和低位的MR非端,同时清为二十四进制。

译码显示

显示器引脚从右到左,1,2,3,4。为了准确的显示出时间,需要用显示器显示出来。右图显示器包含了译码功能,所以无需专门的译码器。正确的引脚连接方式为:Q0接1,Q1接2,Q2接3,Q3接4。

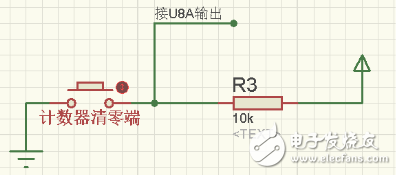

清零复位端

按下清零按钮后计数器清零,数码管显示为1。

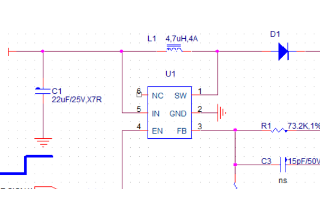

4、24进制计数器电路图

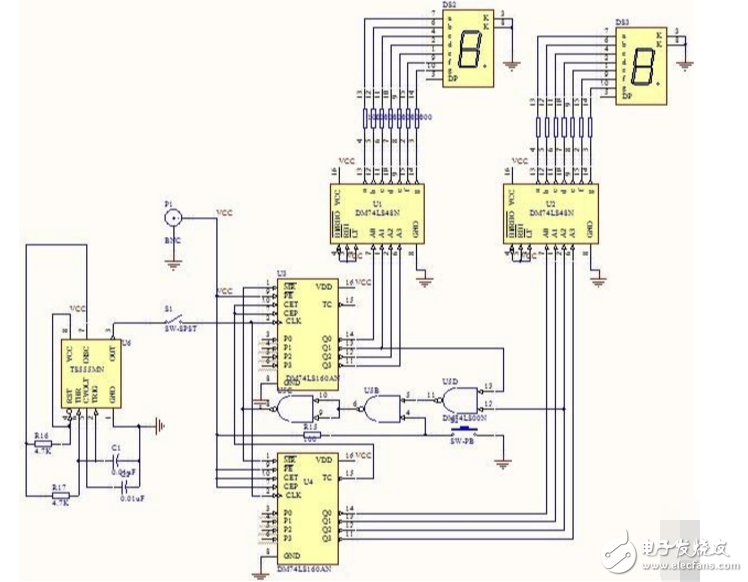

24进制计数器电路(二)

本设计采用异步清零。由两片十进制同步加法计数器74LS160和一片与非门74LS00以及相应的电阻开关组成。

由外加送来的计数脉冲(由555电路产生)送入两个计数器的CLK端,电路在计数脉冲的作用下按二进制自然序依次递增1,当个位计数到9时,输出进位信号给十位充当使能信号进位。当计数到24,这显示器个位输出0010(也就是4),显示器十位输出0010也就是2),显示器十位计数器只有QC端有输出,显示器个位计数器只有QB端有输出,将十位的QC、个位的QB端接一个二输入与非门,与非门输出一路送入十位计数器的清零端,一路送入个位计数器的清零端,将整个电路清零,完成周期为24的计数。

图 24进制计数器电路图

关于74ls160,计数器就介绍完了,您有什么想法可以联系小编。