今天小编要和大家分享的是十路抢答器,抢答器相关信息,接下来我将从十路抢答器电路设计方案汇总(三款模拟+仿真设计电路图),十路智力竞赛抢答器这几个方面来介绍。

十路智力竞赛抢答器

抢答器在各类智力竞赛之中经常出现,它的电路设计并不复杂,本文为大家带来三款十路抢答器电路设计方案。

十路抢答器电路设计方案一:用VHDL设计的十路抢答器

设计内容

(1)设计制作一个竞赛抢答器,共设10个组别每组控制一个抢答开关。

(2)设置主持人控制键,用于控制整个系统清零和抢答有效控制。

(3)主持人发出开始命令,10人开始抢答,其中一人先按下抢答键蜂鸣器会发出鸣叫,指示灯亮,数码管显示该人号码,其他人再按键,系统不再响应,直至主持人按键清零,下一次抢答开始。

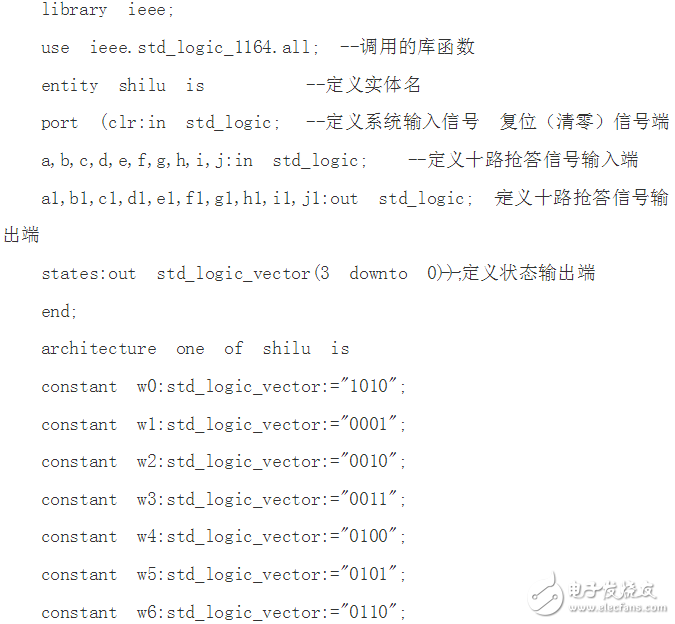

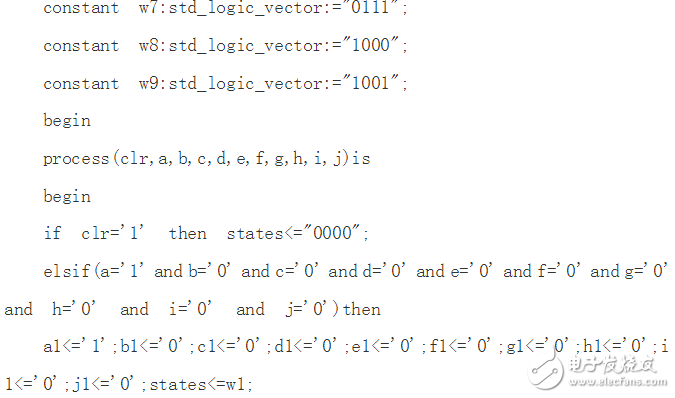

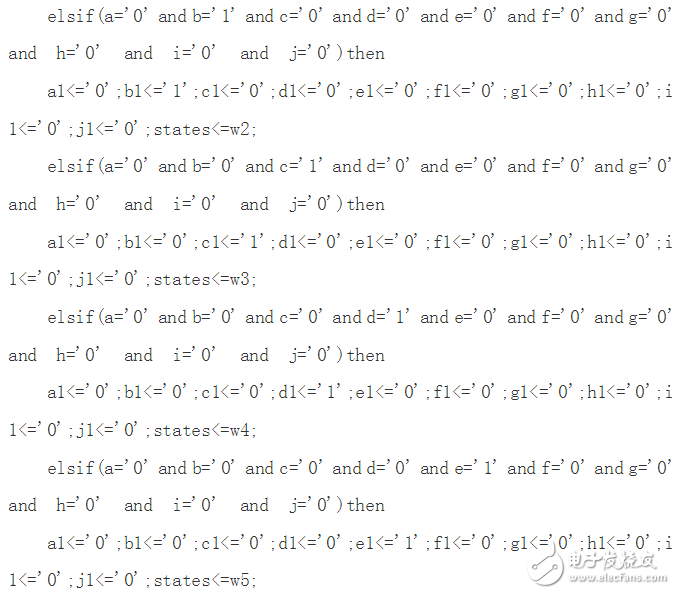

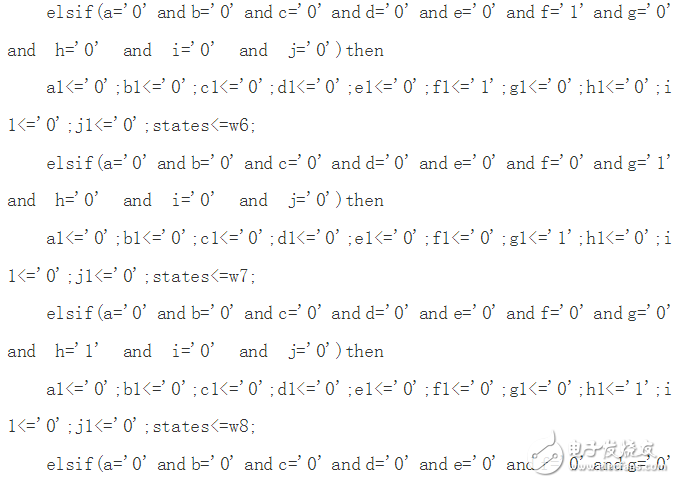

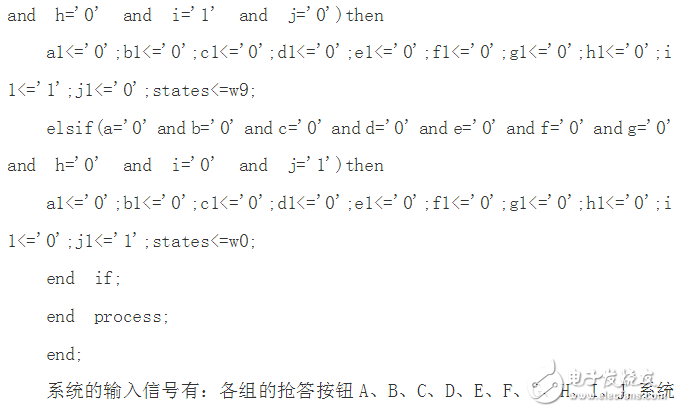

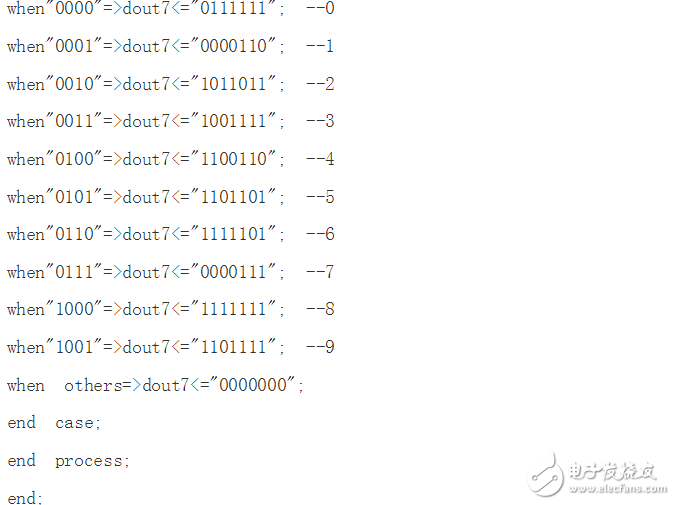

抢答鉴别部分程序

系统的输入信号有:各组的抢答按钮A、B、C、D、E、F、G、H、I、J,系统清零信号CLR。

系统的输出信号有:10个组抢答成功与否的指示灯控制信号输出口A1、B1、C1、D1、E1、F1、G1、H1、I1、J1作为控制蜂鸣器信号。

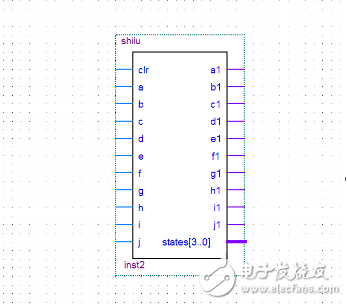

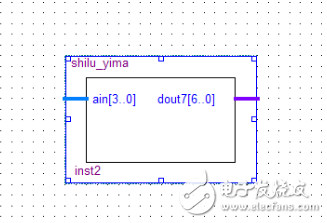

程序打包后如下图:

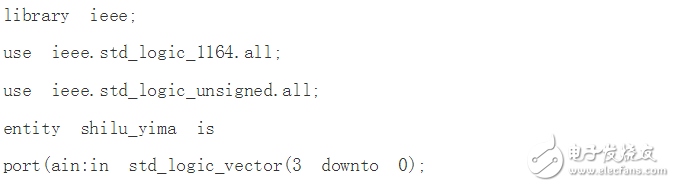

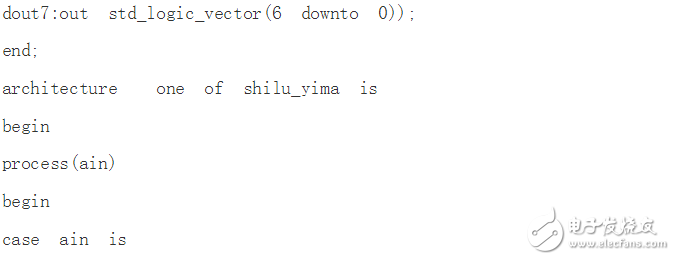

译码显示部分程序

10个组抢答时的数码管显示控制信号DOUT(0-6)。程序打包后如下:

当主持人按下复位按钮CLR时,抢答器开始工作,A、B、C、D、E、F、G、H、I、J10位抢答者谁最先抢答成功则此选手的台灯号将点亮,蜂鸣器提示有抢答者抢答,并且主持人前的组别显示数码管将显示出抢答成功者的台号。接下来主持人提问。完成一轮抢答后,主持人清零复位,接着重新开始下一轮。

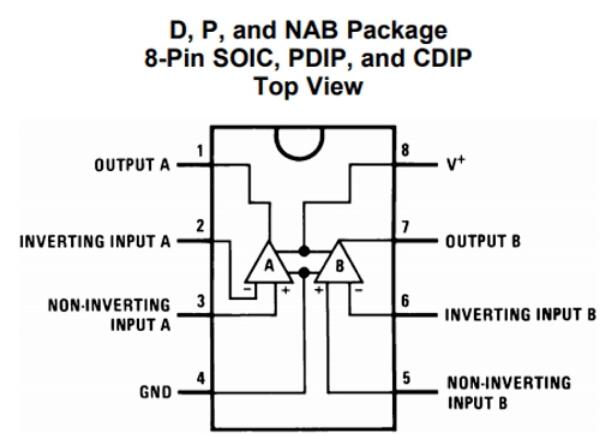

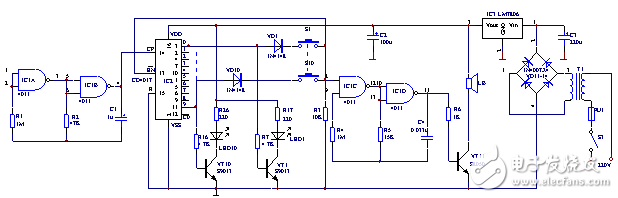

十路抢答器电路设计方案二:基于CD4017和CD4011的十路抢答器

本抢答器由一只CD4017和一只CD4011数字集成电路为核心组成,见下图,其中,CD4011组成两个多偕振荡电路,一个为脉冲分配器CD4017提供计数脉冲,另一个作声音信号发生器用。CD4017在电路中作抢答判决元件,前级计数脉冲接在其上沿触发端CP端,平时其使能端EN通过电阻R4接地,CD4017处于计数状态,其输出端Y0~Y9不断轮流输出高电平,与其相连的发光指示灯被点亮,由于设计时计数脉冲频率较高,各发光管都快速闪烁发光,发光较暗。电路中,抢答器的按钮开关接在发声电路与CD4017的各输出端之间,平时,由于CD4011的C门输入端接地,该发声电路不工作,当按下任一个按钮开关后,电阻R3上的电位上升为高电平,发声电路工作,喇叭发出约500Hz的声音信号。与此同时,CD4017的使能端EN也成为高电平,使其停止计数,被按钮按下的一端保持高电平不变,该端所接发光二极管持续发光,其余发光二极管不再发光,由于一但按钮按下后,只有被按下的输出端保持为高电平,其余都为底电平,因此,以后再按下的按钮均不再起作用,由此作出抢答判决。

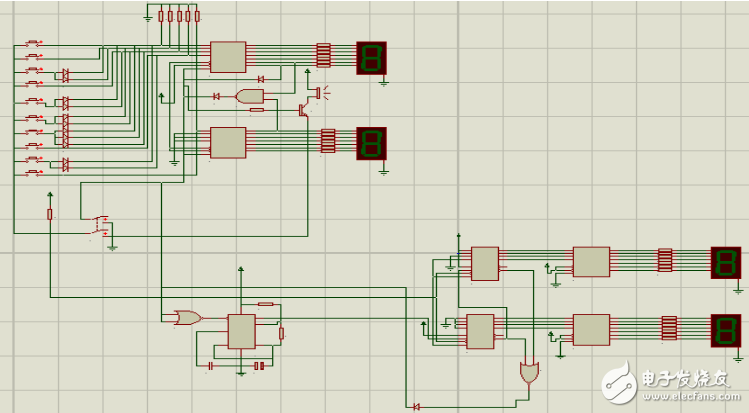

十路抢答器电路设计方案三:十路抢答器设计

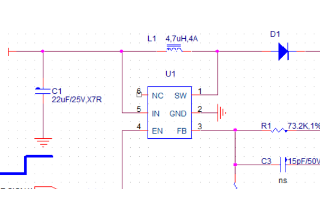

如图所示十路30秒倒计时抢答器的原理图。原理图由倒计时部分和抢答器部分组成。

抢答器部分原理

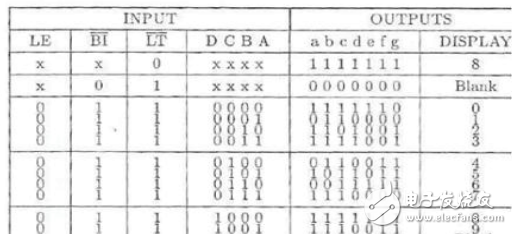

用10个选手按键通过二极管直接控制4511输入端,一旦按键接通,4511则使7段数码管显示相应的数字。初始状态个位和十位数码管均显示“10”,其锁存端电位为0。在显示数字1—9时,十位数码管保持显示“0”,a段输出是高电平,与个位数码管的f端输出进行运算后接入4511的锁存端LE。将个位数码管的g端输出也接至此锁存端。观察4511真值表:

可知,af和g端输出在1—10的显示过程中至少其中之一输出高电平。故,当抢答器部分因为按键的输入导致4511输出使得数码管显示从“00”跳变到“01”—“10”的数字时,使得两个4511连接起来的锁存端电位同时从低电平跳变为高电平,从而实现锁存功能。锁存以后,无论按键如何输入,也不会改变数码管显示,仅当清零按键清零之后才可使锁存端电位置零。

倒计时部分原理

倒计时部分与抢答器部分的连接控制(1)抢答器部分4511的锁存端(2)倒计时部分555的R端。

倒计时部分由555定时器组成多些振荡器,产生时间脉冲,由两片74LS192计数器芯片实现减法计数。当主持人开关打开时,倒计时预置初始数值为30减数至0,当计数至0时,锁存555使振荡器不再输出脉冲,并通过与抢答器部分的连接使抢答器部分4511的锁存端置高电平,因此当计时器从30秒倒计时至0期间无按键输入后,会同时锁存倒计时部分和抢答器部分,知道主持人开关清零为止。

关于十路抢答器,抢答器就介绍完了,您有什么想法可以联系小编。