今天小编要和大家分享的是五人表决器,表决器相关信息,接下来我将从五人表决器电路设计方案汇总(五款模拟电路逻辑图及原理图详解),五人表决器的设计.doc这几个方面来介绍。

五人表决器的设计.doc

本文为大家带来五款五人表决器电路设计方案。

五人表决器电路设计方案一:基于74LS151设计的五人表决器电路

系统原理

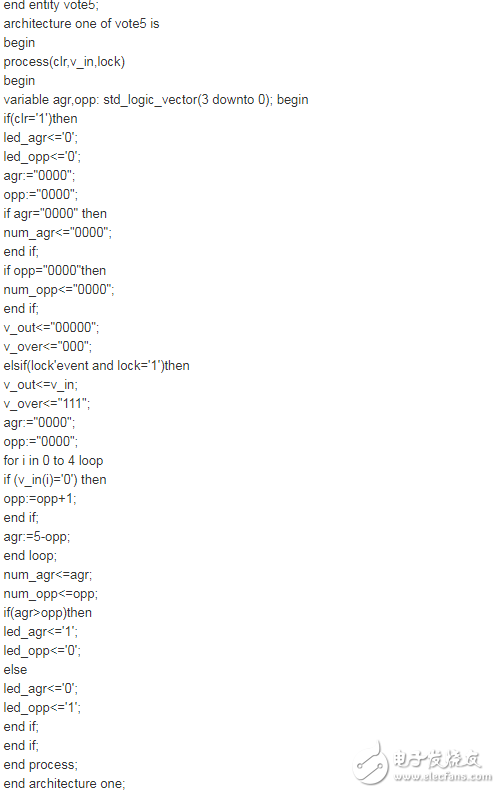

五人表决器,只要赞成人数大于或等于三,则表决通过。因此,只需将每位表决人的结果相加,判断结果值。设五个开关A、B、C、D、E作为表决器的五个输入变量,输入变量为逻辑“1”时,表示表决者“赞成”,红灯亮;输入变量为“0”时,表示表决者“不赞成”,红灯不亮;输出逻辑“1”时,表示表决“通过”,绿灯亮;输出逻辑“0”时,表示表决“不通过”,绿灯不亮;当表决器的五个输入变量中有3个以上(含3个)为“1”时,则表决器输出为“1”,此时绿灯就亮了。

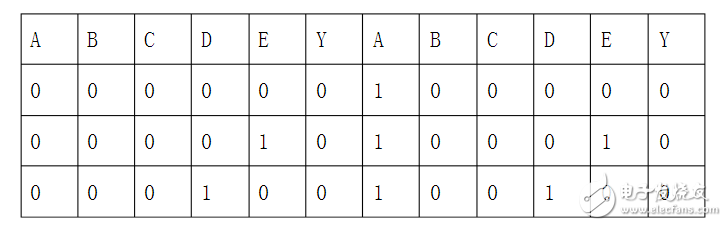

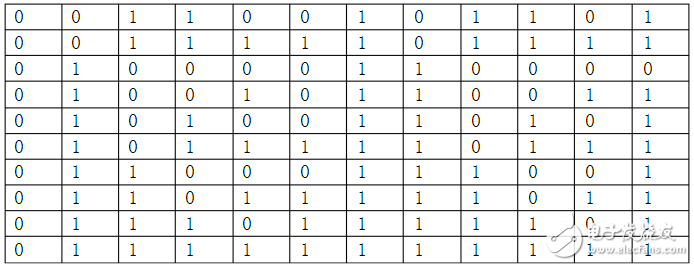

真值表

如果绿灯亮了,则表示表决通过,若绿灯不亮了,表示不通过。

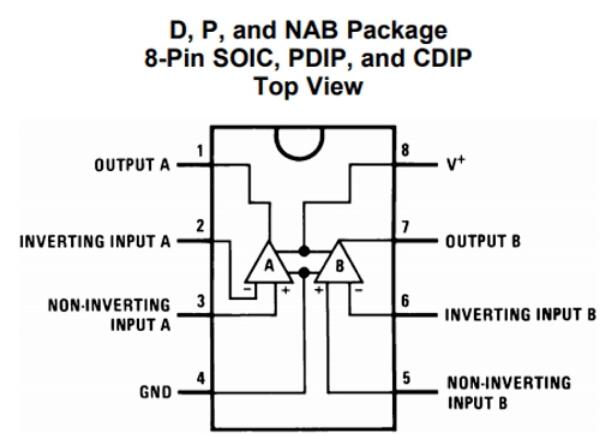

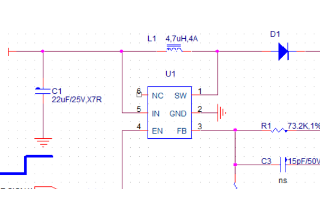

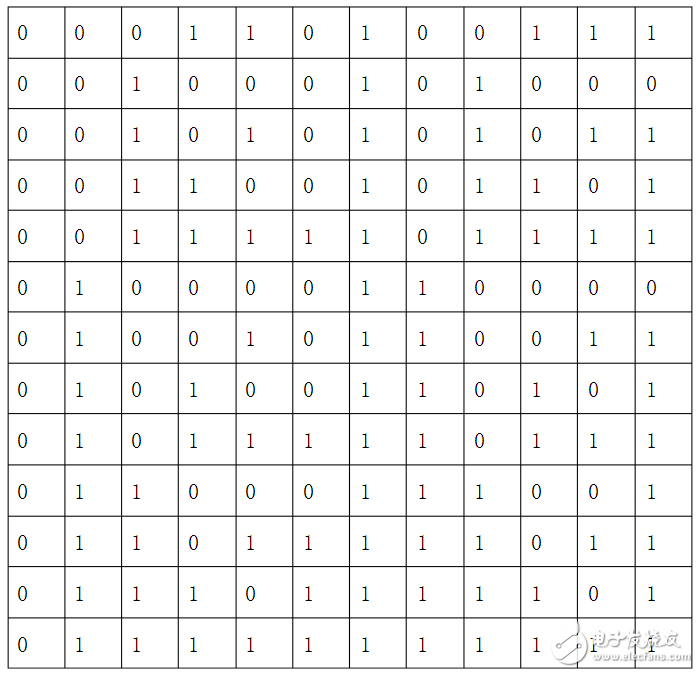

电路设计

原理图

五人表决器电路设计方案二:verilog 五人表决器

程序设计

module vote5(a,b,c,d,e,f);

input a,b,c,d,e;

output f; reg f;

reg[2:0] count1;

initial count1=0;

always@(a,b,c,d,e)

begin

count1《=a+b+c+d+e;

f=count1《3?0:1;

end

endmodule

测试程序

module test;

reg a;

reg b;

reg c;

reg d;

reg e;

wire f;

vote5 uut (

.a(a),

.b(b),

.c(c),

.d(d),

.e(e),

.f(f) );

initial begin

a = 0;

b = 0;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 0;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 0;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 0;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 1;

e = 0;

#100

a = 1;

b = 1;

c = 1;

d = 1;

e = 1;

end

endmodule

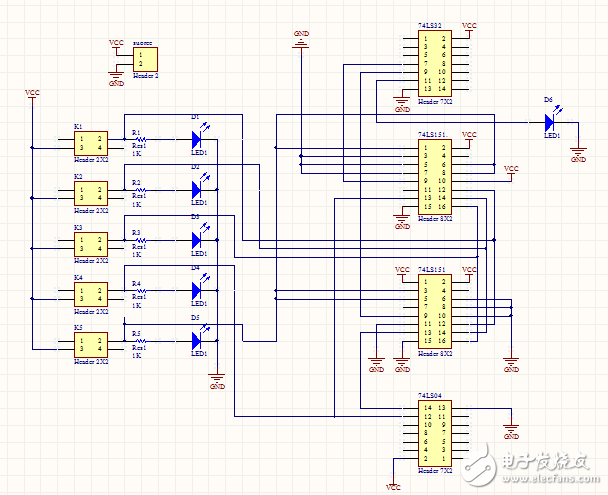

仿真图

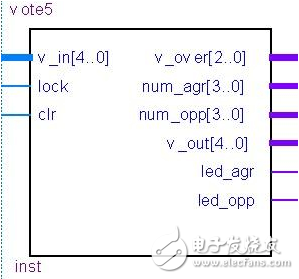

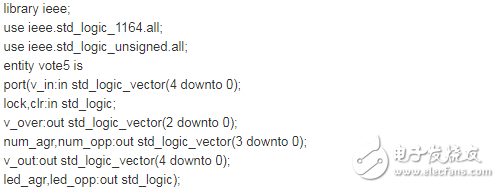

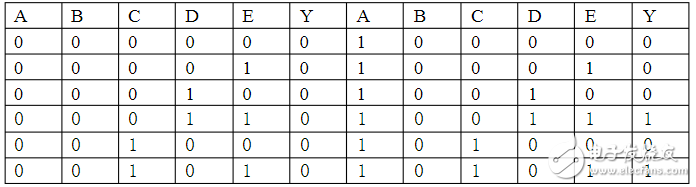

五人表决器电路设计方案三:VHDL编程的五人表决器

用实验平台的LED 发光阵列实现表决结果和每人的表决信号。要求LED1显示判决赞成(led_agr)信号,LED8显示判决反对(led_opp)信号。LED3、LED4、LED5同时显示判决结束信号。LED10、LED11、LED12、LED13、LED14显示5人的表决信号。

当系统启动后,数码管5、6分别显示“FF ”字样,所有用到的数码管熄灭,表决开始,用户此时可以通过拨动开关输入5人的表决意见,并通过LED10~LED14分别显示出来,当用户按下lock 按键(按键6) 后,LED10~LED14的状态被锁存,LED3、LED4、LED5同时点亮,此时无论如何输入表决意见LED10~LED14的状态都不会改变,同时系统会计算出来赞成的人数和反对的人数,并分别用数码管5、6显示出来,而且系统会计算出来赞成的人数和反对的人数的大小关系,并通过LED1和LED8显示出来最终判决的表决结果(判决赞成:LED1亮;判决反对:LED8亮) 。此时用户按下清除键clr(按键7) 后,系统又恢复成为刚启动状态。

源代码

仿真图

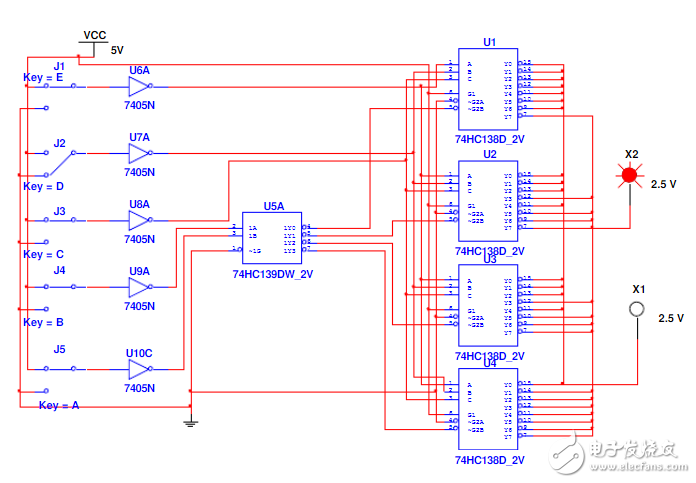

五人表决器电路设计方案四:基于74HC138的五人表决器

对于五人表决器,首先设五人分别为A B C D E 设Y为表决的结果。其中有三人或三人以上同意(同意用“1”表示,不同意用“0”表示)则红灯亮 (红灯用“1”表示),绿灯亮(绿灯用“0”表示)。如果红灯亮了,则表示表决通过,若绿灯亮了,表示不通过。

电路图设计

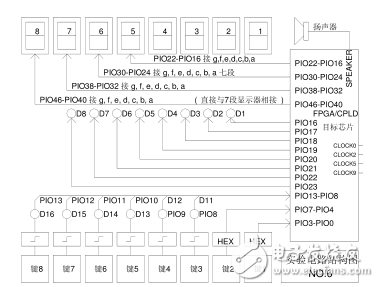

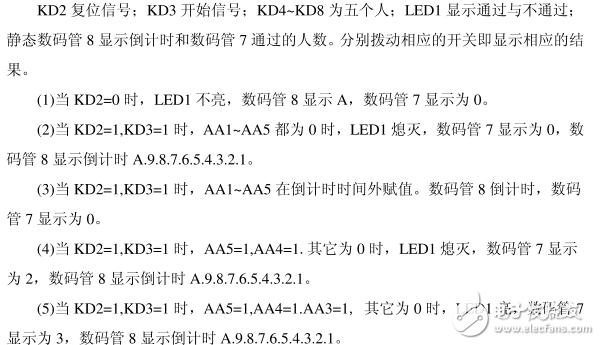

五人表决器电路设计方案五:基于FPGA的五人表决器

电路原理图

此电路图可实现表决器的控制与显示。键8 到键2 分别为五位投票者和复位,开始键。通过数码管显示投票人数,和剩余时间。二极管D8 显示通过与不通过。

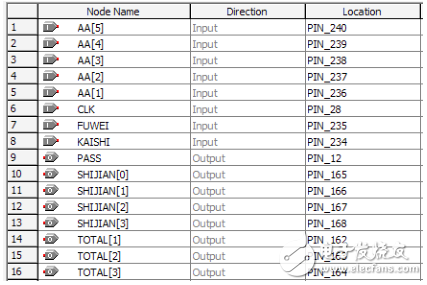

引脚锁定

仿真

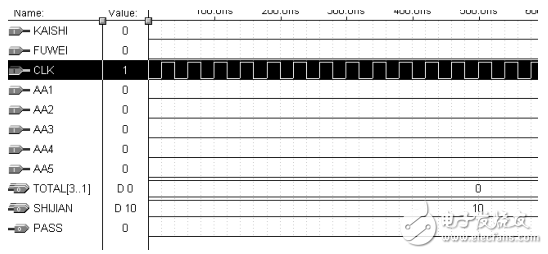

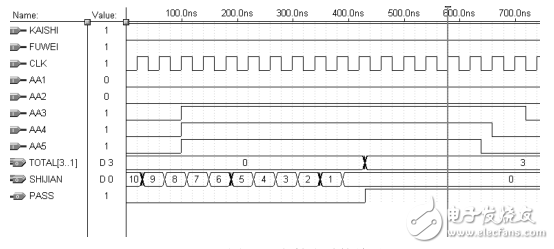

当处于复位状态时,外界的输入对结果没有影响。故时间仍为10 秒,输出统计人数为0。仿真波形如下图所示。

复位时的模拟结果

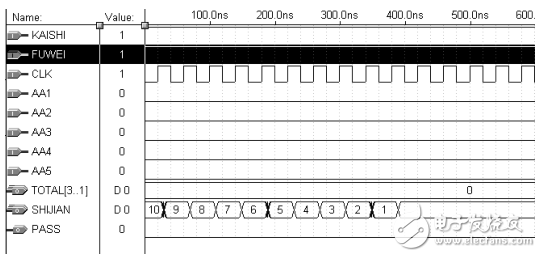

在非复位状态下,主持人按下开始键。表决开始。在没有人投票的情况下。时间变为0。表决结束。仿真波形如下图所示。

无人赞成时的模拟结果

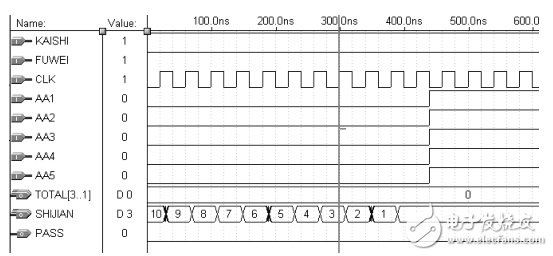

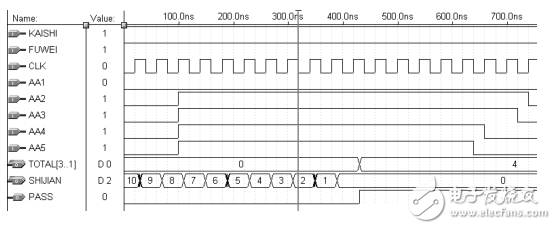

在非复位状态下,主持人按下开始键。表决开始。当超出表决时间时才进行表决,此表决无效。仿真波形如下图所示。

规定时间外的模拟结果

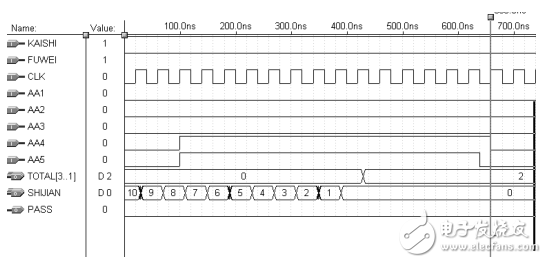

在非复位状态下,主持人按下开始键。表决开始。在规定时间内只有两人赞同。仿真波形如下图所示。

两人赞成时的结果

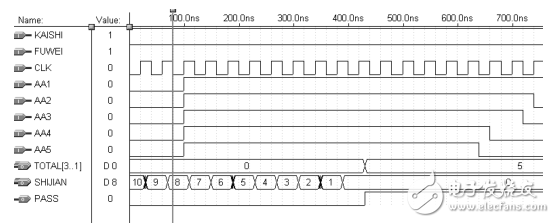

在非复位状态下,主持人按下开始键。表决开始。在规定时间内只有三人赞同。仿真波形如下图所示。

三人赞成时的结果

在非复位状态下,主持人按下开始键。表决开始。在规定时间内只有四人赞同。仿真波形如下图所示。

四人赞成时的结果

在非复位状态下,主持人按下开始键。表决开始。在规定时间内只有五人赞同。仿真波形如下图所示。

五人赞成时的结果

关于五人表决器,表决器就介绍完了,您有什么想法可以联系小编。