今天小编要和大家分享的是74ls161,秒表,计数器相关信息,接下来我将从基于74LS161的简单秒表设计,计数器74ls161功能及其应用ppt这几个方面来介绍。

计数器74ls161功能及其应用ppt

1、引言

在现实生活中,秒表是一种经常运用的器件,特别是在体育竞赛方面,在测试跑步成绩时,除了需要一般的计时功能外还需要具有暂停(记录当前时间)以及复位(清零,为下一次测试做准备)的功能,非常具有实用性。按下启动开始计时,通过2个开关的闭合和关断来实现电路的暂停和复位功能。

2、总体思路

首先,需要了解74LS161的内部器件,以及各个端口所代表的意义,特别是要注意各个功能启动的条件。然后连接电路,由于需要实现0-59,两位数的计数最简单的就是利用2片74LS161,分别显示。利用清零端口对数字进行清零,并且将低位计时器的输出,通过74LS00与74LS20的连接改变0,1关系,作为高位数计时器的输入使用,从而达到目的。其现象和结果通过七段数码管显示。

3、电路设计,仿真

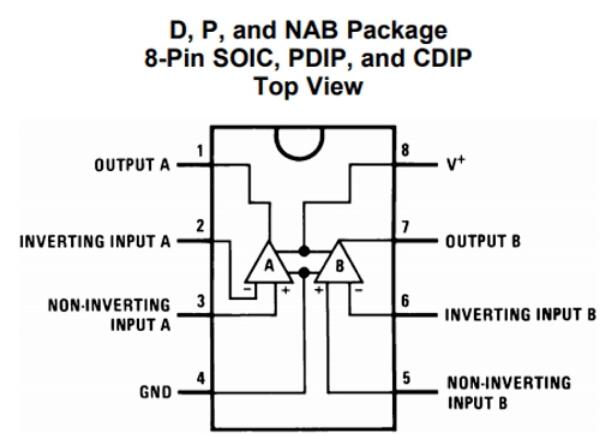

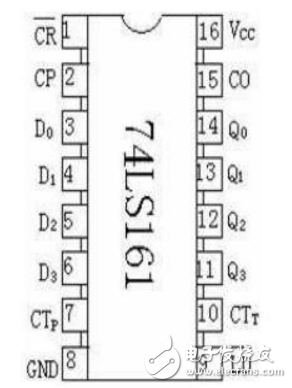

3.1、74LS161(同步二进制加计数器)

74LS161是一种性能比较高,同时能量消耗较小的CMOS4位同步二进制加计数器,可以工作的电压范围是1.2-3.6V,并且在逻辑上输入端可以承受5.5V的电压,所以在仿真中可以直接用5V的电压连接输入端。其工作速度很高,延迟时间仅3.9ns,工作频率最多可达200MHZ,并且工作时的速度很快。

3.2、74LS00和74LS20

74LS00和74LS20虽然都是与非门,但是输入端的数目不同,74LS00一个芯片内有4组二输入的与非门。而74LS20一个芯片内是有2组四输入的与非门。除此之外没有任何区别,同样都是实现先与后非的逻辑关系。

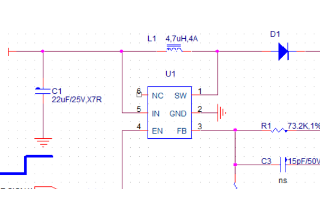

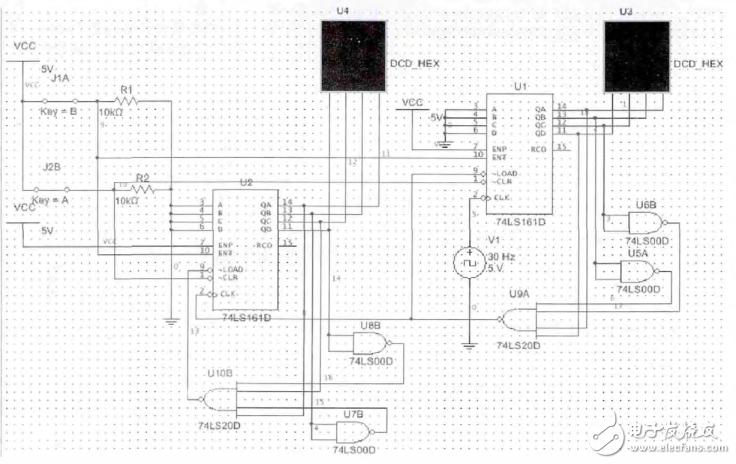

3.3、电路设计和仿真

首先知道74LS161启动的条件,以及清零(复)位的条件还有暂停的条件是什么。其时钟输入端口CP为1时,有时钟输入时,才会启动。而异步清零端口CR则是在外部输入为0时才作用,这是因为系统内部默认的都为1有效,但是在硬件设计上有一个“非”的关系,由于这个关系,变成了外部0有效。暂停则只需要使“使能端”CET(CEP)为0即可实现,产生的数据将会暂停显示在七段数码管上,而不会消失。

从逻辑上看,产生0-59,60个数字。先看个位上,首先是0-9的基本计数,当数字为9时,将会产生进位,在下一个脉冲到来时,十位上的计数器开始启动,显示为1.而个位上的数字9,会清零,并且开始下次的计数,此时十位上的数码管显示为1不变,个位上的计数器继续0-9的计数,当个位数字又变为9时,下一个脉冲时,又会进位,十位上的计时器启动,显示为2,并且保持不变,个位上的计数器开始下一次的

循环计数。当十位数字上的计数器达到5,个位上显示为9时,在下一个脉冲到来时,十位和各位的计数器会同时进行清零(复位)操作。此时又开始从00计数,完成循环计数的目的。

个位的计时器是最先开始计数的,所以需要时钟脉冲来产生信号,其输出为0-9,当输出为9时,换算成二进制码也就是1001,考虑到当各位为9是,十位上的计时器在下一个脉冲到来时要开始计数。而且硬件是用的也是非门,所以是低电平有效,即是说当十位计数器的时钟端口输入为0是,十位上的计数器开始计数。由于使用的是与非门,所以就要使得与非门的输入为0,再连接到十位计数器的时钟端口上。还要考虑到0-8时,不能误操作,所以将最高位和最低位直接连接在74LS20的两端,再将其他两位取反后在接到74LS20的另外两个端口上。此时,当个位上的输出端输出1001时,四输入的与非门的输入就为1111,进行与非关系的运算以后,结果为0,使得十位上的计数器开始计数。完成进位。

图1 简单秒表的仿真连线

再看十位计数器上的清零操作,当计数达到5(0101)时,要求清零,清零操作同样也是低电平有效,所以要使得与非门的输入为1。因此将十位计数器输出端的最低位和次高位直接接在74LS20上,将最高位和次低位取反之后接在另外两个端子上,这样,当计数为5(0101)时,四输入与非门的输入就为1111,取反以后就是0,这是,启动清零(复位)操作。完成要求。仿真如图1所示。

注意图上的取反使用的是与非门,所以讲一个输入分别接在74LS00的两端,就完成了取反的操作。开始运行时,按下开关A,计数会暂停。按下开关B,计数器会清零,重新开始计数。

4、结语

简单秒表的设计是一个很实用的逻辑电路,有多种组合设计的方法,可以使用的元器件也有很多种,74LS161是很基础的一种芯片,使用的范围也比较广泛。这个设计重点在于需要充分理解元件各个端口使用的条件,还有如何正确的将各个端口之间就行连接

关于74ls161,秒表,计数器就介绍完了,您有什么想法可以联系小编。