今天小编要和大家分享的是74LS90,计数器相关信息,接下来我将从浅谈用74LS90设计任意进制计数器,实验7_74ls90任意进制计数器这几个方面来介绍。

实验7_74ls90任意进制计数器

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。计数器可以用来显示产品的工作状态,一般来说主要是用来表示产品已经完成了多少份的折页配页工作。它主要的指标在于计数器的位数,常见的有3位和4位的。很显然,3位数的计数器最大可以显示到999,4位数的最大可以显示到9999。

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,而且常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能,在电路设计中应用相当广泛。文章介绍一种用74LS90设计任意进制计数器的简单方法。

(一)74LS90简介

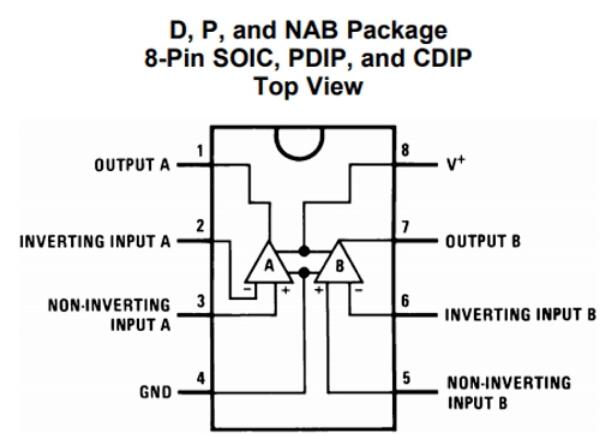

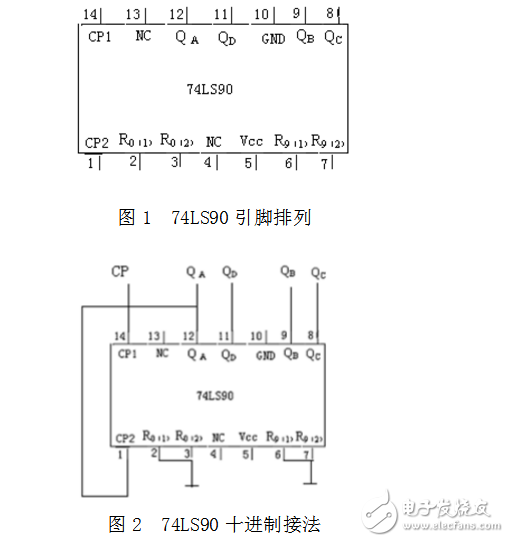

74LS90是二-五-十进制异步加法计数器,具有双时钟输入,并具有清零和置数等功能,其引脚排列如图1所示。

图中

R0(1)、R0(2) 为清零端,两者同时为高电平时实现清零功能,清零方式为异步。

R9(1)、R9(2)为置数端,两者同时为高电平时实现置数功能,此时,输出端输出1001。

QD、QC、 Q B、 Q A为数据输出端。 CP1、CP2为脉冲输入端,其中:

脉冲从CP1进去,输出从QA输出时为二进制记数

脉冲从CP2进去,输出从QD、QC、QB输出时为五进制记数 脉冲从CP1进去,QA接CP2,输出从QD、QC、QB、QA输出时为十进制记数,因此,

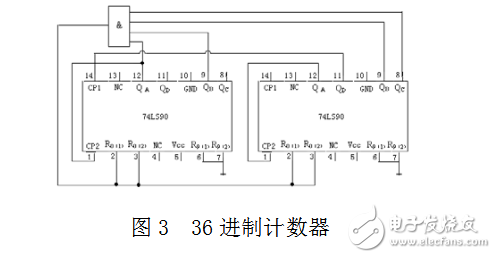

74LS90接成十进制记数方式时的电路如图2。

(二)设计方法

设计采用反馈清零的方法实现,即从0记到要设计的进制时使清零端 R0(1)、R0(2 有效(同时为高电平),进而反馈清零。具体的方法是:如需设计n进制计数器,就把n各位BCD码中为“1”的输出端进行“与”运算,结果接到各个74LS90的R0(1)、R0(2)端,即可实现n进制计数。(因为74LS90是异步清零方式,所以设计n进制计数器则需计到n的BCD码才能返回清零,而不是计到n-1就返回,实际上n只会一闪即失,并不能看到)

(三)实例应用

设计一36进制计数器

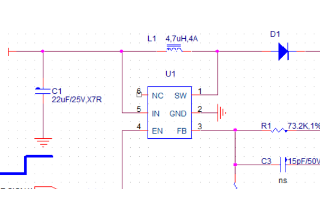

分析:两位数需用2块74LS90,首先将每块接成10进制构成100进制计数器,然后设计计数到36返回清零。36的BCD码为00110110,因此可将十位的QB、QA,个位的QC、QB相“与”,结果接到2块74LS90的清零端。电路:如图3所示。

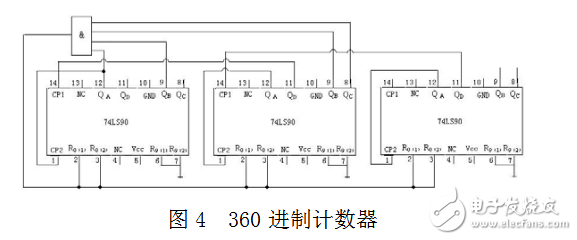

设计一360进制计数器

分析:需用3块74LS90,360的BCD码为001101100000,因此可将百位的QB、QA,十位的QC、QB相“与”,结果接到3块74LS90的清零端。(也可将个位的74LS90按图2接) 电路:如图4所示。

1.设计n进制计数器,n为几位数就需几块74LS90。

2.每块74LS90的两脉冲都按10进制接法接,置数端无效。

3.高位的计数脉冲来自低位的QD。

4.n中为0的那位对应的74LS90的清零端可接n各位BCD码中为“1”的输出端的“与”运算结果,也可接低电(图2接法)

关于74LS90,计数器就介绍完了,您有什么想法可以联系小编。