今天小编要和大家分享的是cd4053,脉冲分解器,模拟开关相关信息,接下来我将从基于集成电路CD4053实现的模拟开关型脉冲分解器的设计,模拟开关芯片 dip-16 cd4053 hef4053bp 个 10 祺好达这几个方面来介绍。

模拟开关芯片 dip-16 cd4053 hef4053bp 个 10 祺好达

主要介绍用集成电路CD4053实现的模拟开关型脉冲分解器

前言

通常所说的脉冲分解器是1种用集成电路结合部分分立器件组装成的单元电路,主要用于将1个脉冲序列中2个不同宽度的脉冲区分开来。实现脉冲分解器的传统方法是用集成单稳触发器、门电路和电阻器、电容器等组成,或者全部使用集成门电路和电阻器、电容器等组成。这样实现的脉冲分解器通常要用几种集成块,而且每片中只用1部分电路,在考虑总体方案时还必须考虑所余电路的应用和走线问题。模拟开关是数字电路的重要组成部分,它的基本功能是作为微功耗电子开关,但采用不同的接线方式,它可能实现几种门电路的功能,也能实现几种时序电路的功能。下面结合1个经典脉冲分解器电路介绍1个用模拟开关CD4053实现的模拟开关型脉冲分解器电路。

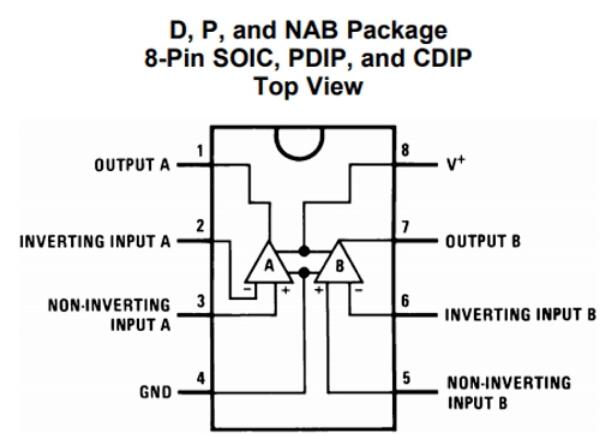

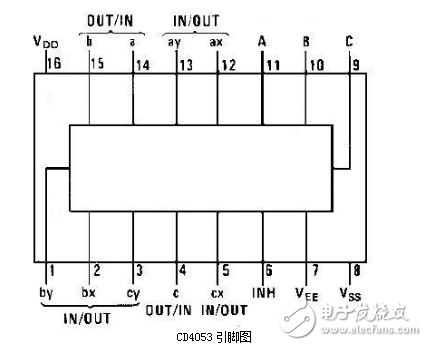

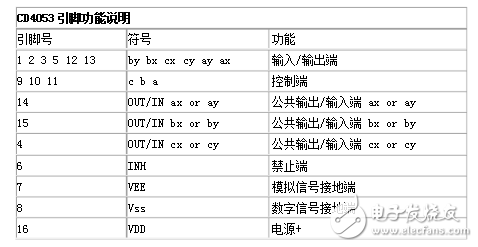

1、CD4053芯片介绍

CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。例如若VDD=+5,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V的模拟信号。这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关。当INH输入端=“1”时,所有通道截止。控制输入为高电平时,“0”通道被选,反之,“1”通道被选。

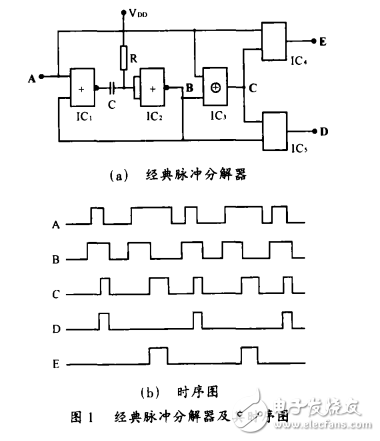

2、经典脉冲分解器

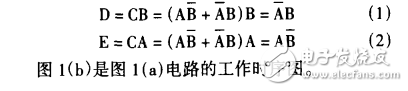

图1(a)示出教科书中的1个经典脉冲分解器电路。IC和IC2(1/2CD4001)是2个或非门,它们和电阻器R、电容器C构成1个单稳触发器,在输人脉冲序列A的触发下产生1个具有一定脉冲宽度的脉冲序列B。选择电阻器R和电容器C的参数,使脉冲序列B的脉冲宽度大于输人脉冲序列A中窄脉冲的宽度,小于脉冲序列A中宽脉冲的宽度。当输人脉冲序列A出现时,就以脉冲序列B为基准,在异或门lC3(1/4CD4070)和与门IC.IC;(1/2CD4081)的帮助下进行逐个比较,在ICS的输出端D输出窄脉冲序列,在IC4的输出端E输出宽脉冲序列。ICS的输出端D和IC的输出端E分别用逻辑式表达如下:

3、模拟开关型脉冲分解器

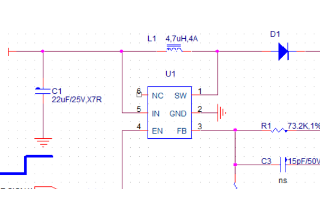

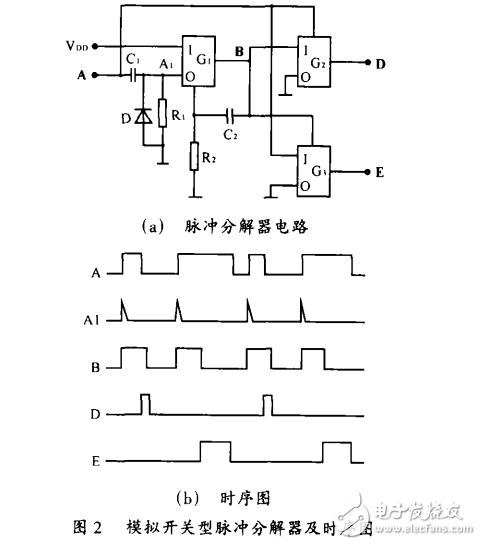

用1只CD4053结合部分立分器件实现的脉冲分解器电路示于图2(a)。在图2(a)中,G1~G3是CD4053中的3个单刀双掷双向模拟开关,0端和1端作为输人端,共用端作为输出端,注意G1、G2、G3控制端接点各不相同,它的1、0两个电平直接控制输出与输人1还是输人0接通。二极管D和电阻器R并联后再和电容器C串联,并接在输人脉冲信号A和地之间,形成1个正脉冲微分电路,将输人脉冲序列A变换成正尖脉冲序列Aio.Gi开关的0输人端接脉冲序列Ai,1输人端接电压Udd,输出端B经电容器C2连接在控制端。电阻器R2并联在控制端和地之间。G1开关和电阻器R2、电容器C2构成1个正脉冲触发并输出正脉冲的单稳触发器。它在脉冲序列A的触发下产生1个具有一定脉冲宽度的脉冲宽度的脉冲序列B。适当地选择电阻器RZ和电容器C2的参数,使脉冲序列B的脉冲宽度小于脉冲序列A中宽脉冲的宽度,大于脉冲序列A中窄脉冲的宽度。G2开关的0输人端接G开关的输出端B,1输人端接地,控制端接输人脉冲信号A.G3开关的0输人端接输人脉冲信号A,1输人端接地,控制端接G1开关的输出端B。图2(b)是图2(a)电路的工作时序图。下面,结合图2(b)简单介绍图2(a)电路的工作原理。

当输入脉冲信号A为0电位时,G1开关的0输入端是地电位,控制端也是地电位,G1开关的输出端B导通在0输入端的地电位。G2开关的0输入端和1输入端都是地电位,故输出端D导通在0输入端B的地电位。B端为地电位,也使G3开关的输出端E导通在0输入端输入信号A的0电位上。

每当输入脉冲信号A出现1个正脉冲时,经过电容器G1和电阻器Ri构成的正微分电路在Ai点就会出现1个正尖脉冲,引起1个单稳延时过程。G1开关输出端B也随0输入端Ai信号上跳1个电位,经电容器C2耦合到控制端,继而使G1开关输出端B导通在1输入端的Udd电位。电压Udd开始经电阻器RZ对电容器C2充电,单稳态电路进入暂稳态延时过程。随着Udd不断对电容器C2的充电,G1开关控制端的电压呈指数方式下降,等到降到转换开关电压Ut时,G1开关的输出端B又回到导通在0输入端的0电位。电容器C2经过G1开关的0输入端,电阻器R1和控制端内部保护电路放电,直到放完。电阻器R1的参数要尽量选小些,以免过分影响放电。

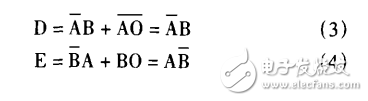

当输入脉冲A刚进入高电位,G1开关的输出端B也刚进入高电位,这时G2开关的输出端D导通在1输入端的地电位,输出电位和初始状态一样。G3开关输出端E导通1输入端的地电位,输出和初始状态一样。假如当前输入脉冲A的脉冲宽度小于单稳延迟时间,则输入脉冲A先前于G1开关输出端B的脉冲回到0电位,从而使G2开关输出端D导通在0输入端B的高电位,G3开关的输出端E仍导通在1输入端的地电位,直到G1开关输出端B回到地电位,G2开关输出端D也随0输入端B回到地电位,开关G3的输出端E又导通在0输入端A的地电位,输出电位恢复到初始电位。假如当前输入脉冲A的脉冲宽度大于单稳延迟时间,则G1开关输出端B的脉冲先于当前脉冲A回到0电位。此时开关G2输出端D仍导通在1输入端的地电位,开关G3输出端E导通在0输入端输入信号A的高电位,直到输入信号A回到0电位,电路又回到初始状态,即E端又导通在0输入端输入信号A的0电位,D端导通在0输入端B的0电位状态。所以D端和E端输出脉冲分别相应于输入脉冲序列A中的窄脉冲和宽脉冲。它们的逻辑表

关于cd4053,脉冲分解器,模拟开关就介绍完了,您有什么想法可以联系小编。