今天小编要和大家分享的是环路滤波器,滤波器相关信息,接下来我将从锁相环环路滤波器设计,cn101546956b_具有环路滤波器的自调节电荷泵有效这几个方面来介绍。

cn101546956b_具有环路滤波器的自调节电荷泵有效

随着通信技术在各个领域的高速发展,频率合成器作为通信设备的重要组成部分,对其也提出了越来越高的设计要求,不但要能满足宽的频率范围、高的频率稳定度和准确度,而且要求其具有良好的杂散和相位噪声、快速的频率切换。

频率合成技术是利用参考频率源来产生具有一系列离散的、高准确度、高稳定度频率信号的一项技术。锁相式频率合成器是利用锁相环(PLL)将压控振荡器(VCO)的频率锁定在某一个频率点上,由压控振荡器产生并输出所需的频率,这种方法输出频率稳定,杂散抑制好,输出频率范围宽。随着锁相环电路集成化、数字化和小型化的不断发展,已经出现了具有快锁功能的锁相环芯片,当前,锁相式频率合成技术得到了最为广泛的应用。环路滤波器是锁相环频率合成器的关键部分,是频率合成器设计中的一个最重要的环节,其参数的合理设计直接关系到频率合成器输出频率信号的杂散、相位噪声、稳定度及频率转换时间等多项指标,间接的影响通信系统的载波质量、接收性能、发射和接收信噪比、接收灵敏度及通信距离等。

1 环路滤波器参数分析

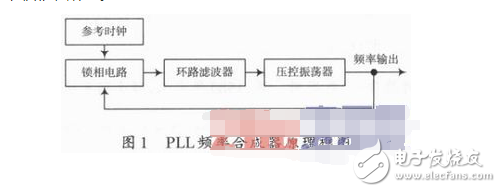

PLL频率合成器的基本框图如图1所示。

环路滤波器是由电阻、电容或者还有放大器组成的线性电路,是一种低通滤波器。它的作用是滤除掉来自PLL电路中鉴相器输出电压Vd(t)中的高频成分和噪声分量,得到一个干净的控制电压Vc(t)去控制压控振荡器的频率输出。环路滤波器包括有源环路滤波器和无源环路滤波器,可根据所选用的锁相环芯片和压控振荡器来确定环路滤波器的形式。

环路滤波器的主要指标包含:环路带宽、锁定时间、直流增益、高频增益和阻尼系数等。其各项参数是根据环路中的VCO增益、电荷泵增益以及鉴相器的分频比而设计的。

环路参数设计中最为重要的参数是环路带宽,环路带宽与参考频率、PFD和环路LP相位噪声成正比关系,它与VCO的相位噪声、锁定时间和分辨率成反比关系。设计中进行环路带宽参数的合理选择有利于VCO的相位噪声、锁定时间、系统分辨率等多项指标的兼顾。

环路滤波器设计中需满足的参数指标高、受到的因素多,设计过程中计算公式复杂,难度较大。ADIsim PLL 3.1仿真软件具有强大的模拟仿真功能,可利用其进行模拟仿真设计,快捷方便、准确合理的设计出稳定的环路滤波器,降低设计过程中的计算量,大大提高设计效率因而在锁相环频率合成技术中得到了广泛的应用。

2 ADIsimPLL 3.1功能介绍

ADIsimPLL 3.1是一款全面的PLL频率合成器设计和仿真工具,此软件具有性能优良的模拟设计能力,其设计环境是基于ADI系列锁相环芯片而设计的,因此,对ADI的锁相环芯片而言,可以充分利用ADIsim PLL 3.1的强大功能,将环路滤波器设计得尽可能完美,而对具有相似功能的频率合成器PLL芯片而言,可以对模拟仿真结果做一些必要的参数调整和修正,对环路滤波器的设计和性能提高也是很有帮助的。总之,ADIsimPLL 3.1设计仿真软件的应用领域是十分广泛的。

ADIsimPLL 3.1设计仿真软件的主要特点有:适用频率范围可达6 GHz;具有整数分频和小数分频两种分频模式可供选择;具有多种的环路滤波器电路形式可供选择;参考频率源可根据需求选择应用;包含丰富的可供选择的PLL芯片;可仿真频率合成器输出的相位噪声及杂散指标结果;对频率转换时间可进行模拟输出;按照仿真结果模拟分析出所需电路的相关元器件参数。

3 环路滤波器的设计应用

实际工作中拟设计一款频率合成器,其相关技术指标要求包括:频率范围满足600~658 MHz;频率间隔为25 kHz;相位噪声满足-90dBc /Hz@10 kHz和-135 dBc/Hz@1 MHz;频率切换时间不大于2 ms。根据设计要求,参考频率源定为10 MHz温补振荡器,其频率稳定度可达6× 10-7,可满足系统所要求的频率稳定度,锁相环芯片选择ADI公司的ADF4156,该芯片具有高达6 GHz的RF输入频率,可满足输出频率范围要求,另外此芯片具有小数分频功能,可实现25 kHz的频率间隔,由于ADF4156芯片的Vp最大值为5.5 V,压控振荡器的压控灵敏度为15MHz/ V,尽可能低的压控灵敏度有利于输出相位噪声指标的提高。

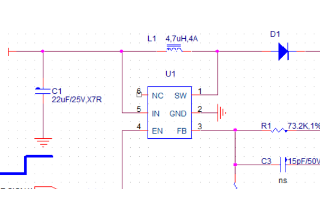

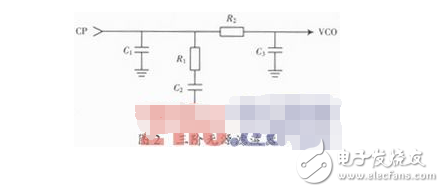

对锁相环电路及压控振荡器选定后,下面进入工作重点,即环路滤波器的设计,设计中根据选择的锁相环ADF4156,环路滤波器选三阶的无源滤波器,电路形式如图2所示。

图2中电容器C1将来自电荷泵(ADF4156的CP脚)的脉冲转化为直流电压,但是根据对开环传递函数分析,它会引起环路的不稳定性,引入了电阻器R1和电容器C2是为了稳定环路,但同时又带来的相应的纹波干扰,电阻器R2和电容器C3能够滤除纹波干扰,同时可以滤除由鉴相频率带来的杂散分量。

设计中环路带宽的参数确定是非常重要的,从环路噪声带宽来看,BL应该选择最小值,从环路稳定性来看,ξ(阻尼系数)越大环路越稳定。由于设计要求中对频率切换时间的要求为不小于2 ms,在环路带宽的选择上可以进行折衷,从而兼顾噪声抑制、频率切换时间和环路的稳定性。

根据设计要求在ADIsimPLL 3.1的设计界面中需要进行各项参数的设置,首先选择PLL芯片ADF4156,进行一系列的参数配置:工作频率范围fmin=600 MHz,fmax=658 MHz;鉴相频率选择fPFD=1 MHz;设置MOD值为8,即可实现的频率间隔;设置VP=5.2 V,最高可设置5.5 V;环路滤波器电路格式选择CPP_3C;压控灵敏度KV=15 MHz/V;参考频率的输入为10 MHz(温补晶体振荡器输入);环路带宽BL设置为5 kHz。

各项参数设置完成后选择“完成”,进行模拟仿真计算,环路滤波器的仿真结果可以清楚地显示出相位噪声曲线、频率切换时间、杂散分布以及环路增益等多项仿真结果,并生成环路滤波器各电阻器和电容器的参数值。最后,可根据工程设计的要求,对相应器件的参数值进行调整,以满足实际应用中工程设计的要求,参数调整过程中,所有仿真结果是可以实时更新的,这样有利于调整过程中对仿真结果的掌握。

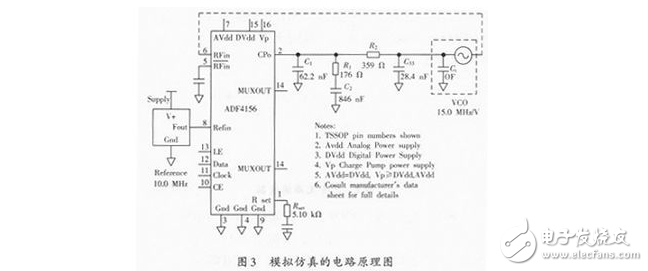

基于以上仿真参数的设置,模拟仿真出的电路原理图如图3所示。

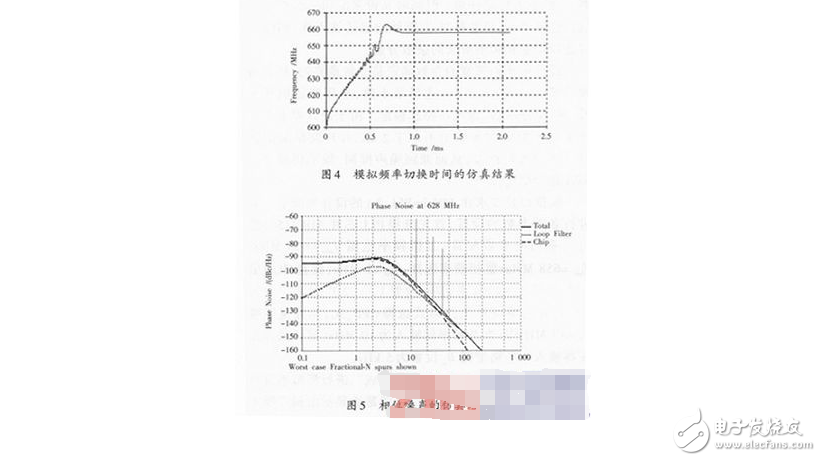

频率切换时间的仿真结果如图4所示。

仿真结果显示,频率转换过程中达到下一频点稳定状态的切换时间为1.26 ms,可满足设计要求中频率切换时间不大于2 ms的要求。

相位噪声的仿真结果如图5所示。

模拟输出的PLL相位噪声为输出频率在628 MHz(中间频率)频率点上的相位噪声曲线,从图中可看到相位噪声分布:-105 dBc/Hz@10 kHz;1 MHz处可优于-160 dBc/Hz,能满足设计要求。

根据仿真结果对PCB(印制电路板)中的环路滤波器进行参数配置,经过装配调试,并与控制电路进行联试及指标测试,电路正常工作,达到了设计预期目标,测试结果与仿真结果基本达到一致,满足频率输出范围600~658 MHz,最大频率切换时间可达到1.45 ms(使用仪器为安捷伦公司的信号综合测试仪E5052B),相位噪声测试结果为-103 dBc/Hz@10 kHz,-155 dBc/Hz@1 MHz(使用仪器为PN9000),杂散指标在全频段范围内可达到-75 dBc,频率稳定度可满足要求(温补晶体振荡器指标保证),频率合成器在要求的温度范围(-40~60℃)各项工作性能稳定。

4 结语

通过利用ADIsimPLL 3.1模拟仿真软件,进行基于ADF4156频率合成器芯片的环路滤波器的成功设计,由理论设计指导工程实际,提高了工作效率,减轻了设计过程中繁重的计算量,始终能够将设计目的和设计过程有效地结合在一起,有助于简捷快速的设计出符合要求的频率合成器的环路滤波器。举一反三,在设计过程中可广泛的应用模拟仿真软件,进行前期的理论分析指导,对实际的设计工作将有很大的帮助。

关于环路滤波器,滤波器就介绍完了,您有什么想法可以联系小编。