今天小编要和大家分享的是超低功耗,多通道ADC,时钟电路相关信息,接下来我将从一种多通道ADC采样板系统电路设计,用于低功耗流水线adc的多模块共享型流水线级电路结构这几个方面来介绍。

用于低功耗流水线adc的多模块共享型流水线级电路结构

ADC板的设计从通道上来划分的话,可以分为单通道ADC板和多通道ADC板,除去有效位数、动态范围、最大采样率以及输入带宽等一些基本参数以外,多通道ADC板相对于单通道ADC板来说,往往还要衡量通道间幅度一致性和通道间相位一致性,这也正是多通道ADC板设计的一个难点。为了满足四路ADC之间通道间幅度一致性和通道间相位一致性的指标要求,首先需要将四路ADC芯片的采样时钟做到尽可能同步,实现四路ADC芯片对输入中频信号的同步采集。为此,本设计采取了把外部输入采样时钟通过同一时钟驱动芯片分发后送给四路ADC芯片作为同步采样时钟的方式,在时序上保证了四路ADC芯片采样时钟的同步。

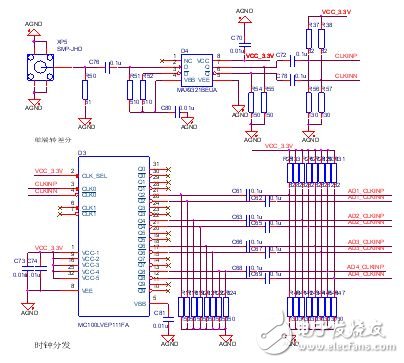

时钟分发单元电路设计

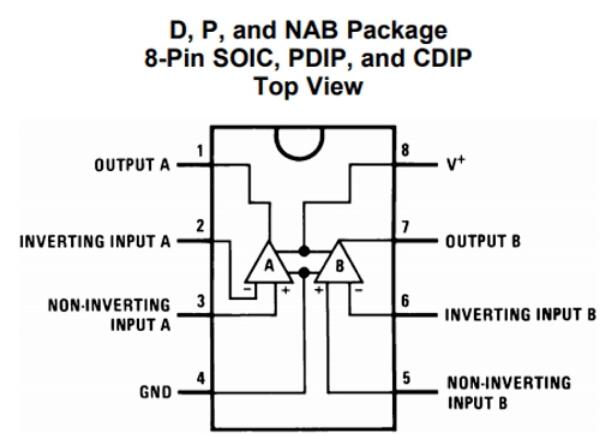

时钟分发单元需要差分时钟输入,而外部输入时钟信号为单端信号,因此外部时钟在进入时钟分发单元之前首先需要进行单端信号到差分信号的转换,此处采用MAX9321BEUA芯片完成了把外部输入单端时钟转变为差分时钟的功能。时钟分发单元采用MC100LVEP111FA芯片,此芯片为1:10路低偏移差分时钟驱动芯片,各引脚之间的输出到输出偏移典型值仅为20ps,并且所产生的抖动非常小。通过此芯片理论上实现了四路ADC芯片采样时钟的同步。时钟分发单元的具体原理图如图2所示。

图2 时钟分发单元原理图

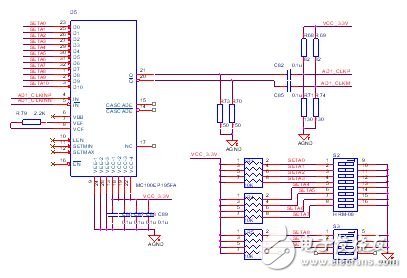

可调时钟延迟单元电路设计

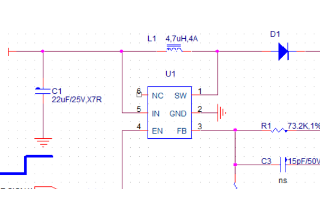

由于芯片制造工艺以及实际电路板设计等各种客观因素的存在,外部时钟实际到达四路ADC芯片的时间相差可能大于理论值,造成了四路ADC采样时钟满足不了同步的要求,进而影响四路ADC芯片间的通道间幅度一致性和通道间相位一致性。为此,在每一路采样时钟到达ADC芯片之前增加了可调时钟延迟单元。可调时钟延迟单元可以调节每一路时钟信号的延迟时间,修正四路ADC采样时钟之间的相对延迟,从而实现了四路ADC采样时钟的同步。其中一路可调时钟延迟单元的原理图如图3所示。

图3 可调时钟延迟单元原理图

上述可调时钟延迟单元采用了MC100EP195FA芯片,该芯片是可编程延时单元,可以选择10ps为延迟时间单位递增,最大延迟时间可达到 10ns。具体来说就是通过对此芯片配置不同的D[9:0]值,得到不同的延迟时间。通过调节时钟延迟单元可以保证四路ADC采样时钟的同步采集。时钟延迟单元部分的延迟时间配置值。

本文设计的四通道ADC已经得到成功使用,实际所测通道间幅度一致性小于0.5dB;通道间相位一致性小于5。ADC的有效位数为9.8bit,满足了设计的需求。本文提供了一种多通道ADC设计的思想,为满足通道间幅度一致性和通道间相位一致性的要求,需要各通道ADC采样时钟的同步。实际证明,采用时钟延迟单元是一种保持多通道采样时钟同步的简单易行的方式。

关于超低功耗,多通道ADC,时钟电路就介绍完了,您有什么想法可以联系小编。