今天小编要和大家分享的是FPGA,锁相环相关信息,接下来我将从基于FPGA的锁相环位同步提取电路,数字锁相环的fpga设计与实现ppt这几个方面来介绍。

FPGA,锁相环相关技术文章基于FPGA的锁相环位同步提取电路

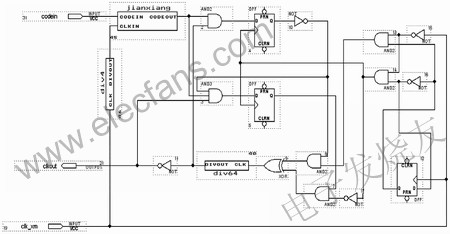

基于fpga的锁相环位同步提取电路

该电路如图所示,它由双相高频时钟源、过零检测电路、鉴相器、控制器和分频器组成。

欢迎转载,本文来自电子发烧友网(http://www.elecfans.com/)

关于FPGA,锁相环就介绍完了,您有什么想法可以联系小编。

今天小编要和大家分享的是FPGA,锁相环相关信息,接下来我将从基于FPGA的锁相环位同步提取电路,数字锁相环的fpga设计与实现ppt这几个方面来介绍。

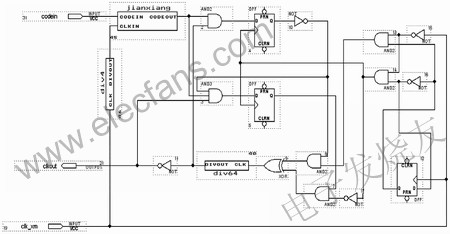

FPGA,锁相环相关技术文章基于FPGA的锁相环位同步提取电路

基于fpga的锁相环位同步提取电路

该电路如图所示,它由双相高频时钟源、过零检测电路、鉴相器、控制器和分频器组成。

欢迎转载,本文来自电子发烧友网(http://www.elecfans.com/)

关于FPGA,锁相环就介绍完了,您有什么想法可以联系小编。

上一篇:分频与倍频电路图

下一篇:彩印冲洗恒温器电路图