i.MX28系列处理器内部集成以太网控制器MAC(Media Access Controller)(i.MX283集成1路,i.MX287集成2路)。如图1所示,想要实现完整的以太网通信功能,还需要以太网收发电路(PHY)、以太网连接电路,与以太网控制器MAC共同组成以太网通信的物理层和数据链路层。

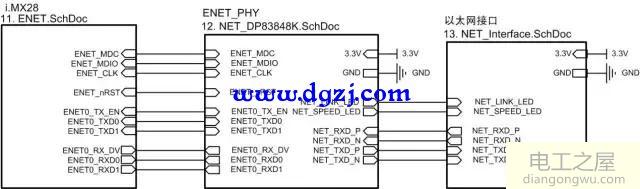

图1 以太网电路结构

i.MX28以太网控制器支持10/100 Mbps的RMII与MII接口。RMII接口收发数据信号线比MII接口均减少一半,接口简单。为了节省I/O资源,EasyARM-i.MX283(7)A采用了RMII接口与以太网PHY连接,接口应用电路如图2所示。

图2 以太网应用电路框图

以太网收发器电路

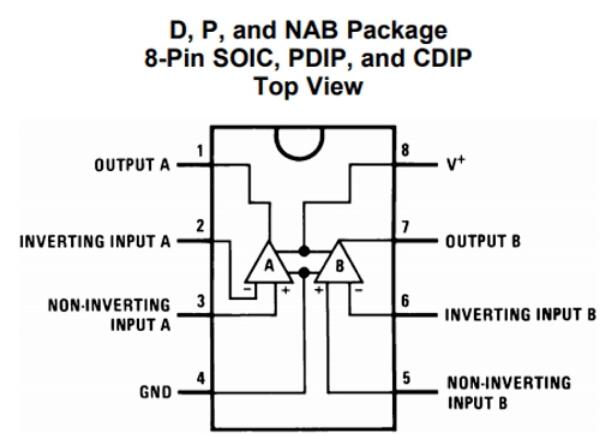

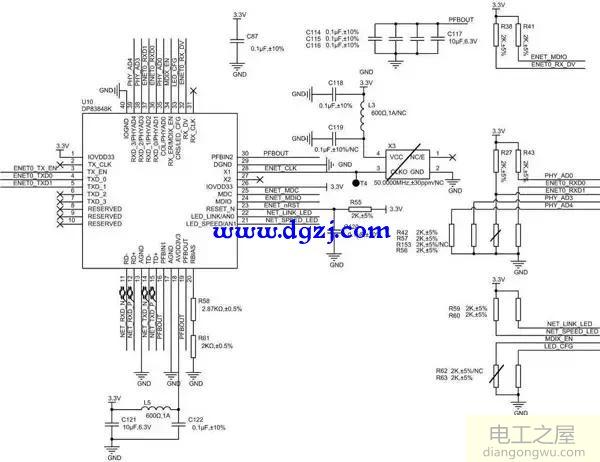

EasyARM-i.MX283(7)A使用TI公司的DP83848J作为以太网收发芯片(以太网PHY芯片),引脚说明见表1。该芯片是单端口10/100M以太网收发器,支持MII/RMII接口,支持2个LED指示连接状态和速度。处理器MAC与PHY通过RMII接口相连。使用RMII接口时,需要为以太网收发电路(以太网PHY芯片)提供50MHz的参考时钟,该时钟可以由CPU提供,也可以外接50MHz的有源晶振,EasyARM-i.MX283(7)A中默认由CPU提供。

表1 DP83848J引脚说明

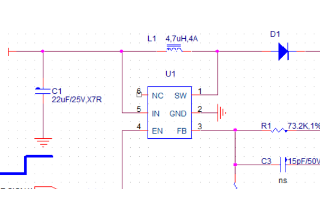

如图3所示,为DP83848J电路。对照表4.3的引脚说明可知,PHY地址默认配置为0x05(可通过去除电阻R153,配置为0x01),接口模式配置为RMII。EasyARM-i.MX283(7)A设计时保留有源晶振的焊盘,用户如果需要使用外部晶振为以太网PHY提供时钟信号,可自行焊接。PCB 设计时以太网设计PHY至I.MX28芯片的RMII线要做等长处理,PHY至芯片的RMII走线应尽量短,并且总长度建议不要超过2英寸(5.08cm);

图3 以太网收发器电路