今天小编要和大家分享的是powerpcb相关信息,接下来我将从PCB优化设计详析(中),专业pcb电路板打样,单面板价格优惠了双面满3个平米不这几个方面来介绍。

powerpcb相关技术文章PCB优化设计详析(中)

PCB优化设计详析(中)

目前SMT技术已经非常成熟,并在电子产品上广泛应用,因此,电子产品设计师有必要了解SMT技术的常识和可制造性设计(DFM)的要求。采用SMT工艺的产品,在设计之初就应综合考虑生产工艺流程、原材料的选择、设备的要求、器件的布局、测试条件等要素,尽量缩短设计时间,保证设计到制造的一次性成功。

关键词 SMT PCB DFM 优化设计

3.5 元器件布局设计

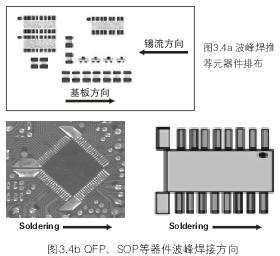

元器件的布局是按照原理图的要求和元器件的封装,将元器件整齐、美观的排列在PCB上,满足工艺性、检测、维修等方面的要求,并符合电路功能和性能要求。进行元器件布局设计时要做到工艺流程最少,工艺性最佳。元器件布局设计的基本原则如下:(1) 元器件的排布均匀,尽可能做到同类元器件按相同的方向排列,相同功能的模块集中在一起布置;相同结构电路部分应尽可能采取对称布局。(2) 元器件布局遵照“先难后易,先大后小”的布置原则,即重要的单元电路、核心元器件应当优先布局,其他元器件围绕它来进行布局。(3) 有相互连线的元器件应靠近排列,以保证走线距离最短,有利于提高布线密度。(4) 缩短高频元器件之间的连线,减少它们的分布参数和相互间的电磁干扰。易受干扰的元器件应隔离或屏蔽。(5) 对于热敏感元器件(除温度检测元件),布线时应远离发热量大的元器件。发热元件一般应均匀分布,排布在通风、散热良好的位置,以利于单板和整机的散热。(6) 强信号和弱信号、高电压信号和弱电压信号要完全分开;模拟信号和数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分。(7) 热容量大的元器件排布不宜过于集中,以免局部温度低造成焊接不良。(8) 对于电位器、可调电感等可调元器件的布局应考虑整机的结构要求。若在机内调节,应放在PCB上方便于调节的地方;若在机外调节,其位置要与调节旋钮在机箱面板上的位置相适应。(9) 元器件的排列要便于调试和维修,QFP、BGA、PLCC等器件周围要留有一定的维修空间。(10) 高大、贵重元器件不要放在PCB边缘或靠近插件、贴装孔、槽、V-CUT等高应力集中区,减少开裂或裂纹。(11) 要考虑插座、接头等元器件之间是否干涉,与结构设计是否矛盾。(12) 同类型的插装元器件在X或Y方向上应朝一个方向放置。同类型的有极性插装元器件尽量在X或Y方向上保持一致,便于生产和检验,同一块板最多允许2个方向。(13) 焊接面的贴装元件采用波峰焊接生产工艺时,阻、容器件的长轴方向要与波峰焊传输方向垂直,阻排及SOP(脚间距≥1.27mm)元器件长轴方向与波峰焊传输方向平行,间距<1.27mm的SOP、PLCC、QFP等元器件避免用波峰焊焊接,BGA、CSP、QFN等元器件严禁采用波峰焊接。如下页图3.4a所示。QFP器件应按照45度方向排布,并增加盗锡焊盘。SOP等器件也应该增加脱锡焊盘。如下页图3.4b示。较小元器件不应排在大元件后,以免较大元器件遮挡锡流与较小元器件焊盘接触,造成漏焊。

(14) 回流焊接和波峰焊接工艺对元器件布局限制。不同的SMT组装工艺,对元器件布局有不同的要求,例如0402封装的元器件可以回流焊接但不适合波峰焊接。具体请参考下表3-5。

3.6 PCB布线设计

布线是按照原理图和导线表布设PCB导线,布线的一般原则如下:(1) 布线优先次序密度优先原则:从PCB上连接关系最复杂的器件着手布线,从PCB上连线最密集的区域开始布线。核心优先原则:例如DDR、RAM等核心部分应优先布线,类似信号传输线应提供专层、电源、地回路。其他次要信号要顾全整体,不可以和关键信号想抵触。关键信号线优先原则:电源、模拟小信号、高速信号、时钟信号和同步信号等关键信号优先布线。布线层数选择原则:在满足使用要求的前提下,选择布线的顺序优先为单层布线,其次为双层布线,最后是多层布线。(2) 尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其最小的回路面积。应采取手工优先布线、屏蔽和加大安全间距等方法,保证信号质量。(3) 电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号。(4) 有阻抗控制要求的网络应布置在阻抗控制层上,相同阻抗的差分网络应采用相同的线宽和线间距。对于时钟线和高频信号线要根据其特性阻抗要求考虑线宽,做到阻抗匹配。(5) 输入输出端用的导线应尽量避免相邻平行。最好加线间地线,以免发生反馈藕合。(6) 数字地、模拟地要分开,对低频电路,地应尽量采用单点并联接地;高频电路宜采用多点串联接地。对于数字电路,地线应闭合成环路,以提高抗噪声能力。(7) 印制导线拐弯处一般取圆弧形,而直角或夹角在高频电路中会影响电气性能。(8) 走线拐弯处一般取圆弧形,避免直角或夹角,否则在高频电路中会影响电气性能。如图3.6所示。

(9) 导线的最小宽度主要由导线与绝缘基板间的粘附强度和流过它们的电流值决定。导线的最小间距主要由最坏情况下的线间绝缘电阻和击穿电压决定。(10) 双面板上的公共电源线和地线尽量放置在靠近板的边缘,并且分布在板的两面。多层板可在内层设置电源层和地线层,通过金属化孔与各层的电源线和地线连接。(11) 焊盘与较大面积的导电区相连时,应采用长度不小于0.5mm的细导线进行热隔离,细导线宽度不小于0.13mm。(12) 相邻层信号线为正交方向,以减少耦合,切忌相邻层走线对齐或平行。

3.7 PCB的孔设计

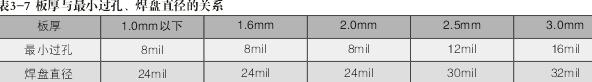

PCB上常见的孔有安装孔、定位孔、元件孔、导通孔、盲孔和埋孔、测试孔等。(1) 安装孔(Mounting Hole)安装孔用于装配器件,或固定印制板,安装孔应与安装器件的位置尺寸和公差相匹配。(2) 定位孔(Tooling Hole)定位孔是放置在板边缘上的用于电路板生产和装配的非金属化孔。具体见3.3条。(3) 元件孔(Component Hole)元件孔是用于元件端子固定于印制板及导电图形电气联接的孔。元件孔的孔径应比所安装的元器件引线直径大0.2~0.3mm。(4) 导通孔(Via Hole)导通孔又称过孔,一种用于内层连接的金属化孔,但其中并不用于插入元件引线或其它增强材料。孔径大小和空位可根据布线空间大小调整,一般孔径取Φ0.3~Φ0.8mm,金属化孔的电阻值不超过300μΩ。PCB板厚决定了该板的最小过孔,板厚孔径比应小于5~8,如下表3-7所示。

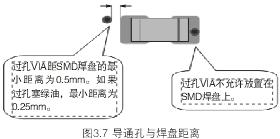

在布线空间允许的条件下,导通孔一般不放在元器件的下面,以便于检查和维修。导通孔与SMD的焊盘最小距离为0.5mm,如果过孔塞绿油,最小距离为0.25mm。如图3.7所示。

(5) 盲孔(Blind via)和埋孔(Buried via)盲孔是连接表层和内层而不贯穿的过孔,埋孔是连接内层而表层看不到的过孔。应用盲孔和埋孔设计时应对PCB加工流程有充分的认识,避免给PCB加工带来不必要的问题,必要时要与PCB供应商协商。(6) 测试孔(Test Pattern)测试孔是指用于ICT测试目的的过孔,可以兼做导通孔,原则上孔径不限,焊盘直径应不小于25mil,测试孔之间中心距不小于50mil。

3.8 可测试性设计

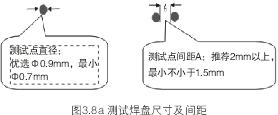

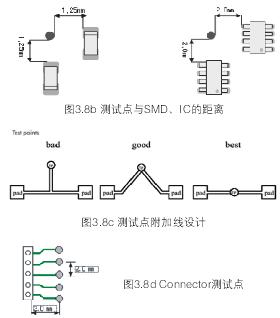

SMT的测试包括在线测试(In-Circuit Testing,ICT)和功能测试(Function-Circuit Testing,FCT)。为保证大批量生产的产品的质量,需要使用ICT和FCT,其中SMT的可测试性主要是针对ICT的。在PCB设计阶段一定要考虑添加测试点,相关设计要求如下:(1) 测试点均匀分布于整个PCB 板上,一般要求每个网络都要至少有一个可供测试探针接触的测试点。(2) 测试点选用时优先次序:优选圆形焊盘;其次器件引出管脚;最后过孔最为测试点。SMD器件最好采用圆形焊盘做测试点,OSP处理工艺的PCB不宜采用过孔做测试点。当使用表面焊盘作为测试点时,应当将测试点尽量放在焊接面。(3) 测试焊盘尺寸最小为0.6mm,当有较多PCB的富裕空间时,测试焊盘设定为0.9mm以上。两个单独测试点的最小间距为1.5mm,推荐值2.0mm。如图3.8a所示。

(4) 测试点不能被丝印盖住,丝印通过时会发生接触不良。测试点不能被条码、胶带等挡住。(5) 测试点与SMD的距离至少1.25mm,测试点与IC器件的距离至少2.0mm,测试点与DIP插件孔的距离1.25mm。测试点距离板边不得小于5mm。如图3.8b所示。(6) 测试点在添加时,附加线应该尽量短。如图3.8c所示。(7) 采用圆形焊盘作为测试点时,如果PCB表面处理工艺为OSP,建议测试焊盘上印刷锡膏,以加强测试的可靠性。(8) 对Connector器件,若引线较粗或Pitch≤1.5mm时,需要单独引出测试点。如图3.8d所示。(9) 对于带有边界扫描(Boundary-Scan)器件的VLSI和ASIC器件,应增加为实现边界扫描功能的辅助测试点,以达到能测试器件本身的内部功能逻辑的要求。

3.9 PCB散热设计

随着SMD的外形尺寸变小,组装密度提高,若不能及时有效的散热,将会影响电路的工作参数甚至会使元器件失效,因此必须考虑散热设计。(1) 高热器件应考虑放于出风口或利于对流的位置,较高的元件应考虑放于出风口,且不阻挡风路。(2) 散热器的放置应考虑利于对流。(3) 发热量大的元器件架高设计,温度敏感器件应考虑远离热源。(4) 对于自身温升高于30℃的热源,一般要求:a.在风冷条件下,电解电容等温度敏感器件离热源距离要求≥2.5mm;b.自然冷条件下,电解电容等温度敏感器件离热源距离要求≥3.0mm。(5) 大面积铜箔要求用隔热带与焊盘相连。为了保证透锡良好,在大面积铜箔上的元件的焊盘要求用隔热带与焊盘相连,对于需过5A以上大电流的焊盘不能采用隔热焊盘。如图3.9所示:

(6) 设置散热通孔,可以有效地将热量从PCB的顶部铜层传输到内部或底部铜层。

3.10 抗电磁干扰设计

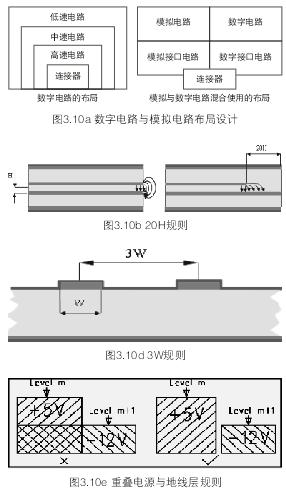

电磁干扰问题越来越成为电子产品中的一个严重问题。经验表明,产品批量生产后电磁干扰问题的解决成本是开发阶段解决成本的十几倍,甚至几十倍,因此电磁兼容设计应该贯穿电子产品设计的全过程。常用的电磁兼容设计方法有:(1) 从减小辐射干扰的角度出发,应尽量选用多层板。内层分别做电源层、接地层,电源层与地线要尽量靠近,时钟线、信号线和地线位置尽量靠近,以获得最小接地线路阻抗,抑制公共阻抗噪声。对信号形成均匀的接地面,加大信号线和接地面间的分布电容,抑制其向空间辐射的能力。(2) 电源线、地线、印制板走线对高频信号应保持低阻抗,在频率很高的情况下,电源线、地线或印制板走线都会成为接收与发射干扰的小天线,降低这种干扰的方法除了加滤波电容的方法外,更值得重视的是减少电源线、地线、印制板走线本身的高频阻抗。因此,各种印制板走线要短而粗、线条要均匀。(3) 为减少信号线与回线之间形成环路面积。电源线、地线、印制板导线的排列要恰当,尽量作到短、宽、直。走线时应避免产生锐角和直角,产生不必要的辐射,同时工艺性能也不好。(4)当线路板上有不同功能电路时,不同类型电路(数字、模拟、电源)应分离,其接地也应分离。如图3.10a所示。(5) 对于多层线路板,不同区域的地线面在边远处要满足20H法则(即地线面的边沿要比电源层或信号线层的边沿外延出20H,H是地线面与信号线层之间的高度)。如图3.10b所示。

(6) 3W原则。当两条印制线间距比较小时,两线之间会发生电磁串扰,串扰会使有关电路功能失常。为避免发生这种骚扰,应保持任何线条间距不小于三倍的印制线条宽度,即不小于3W,W为印制线路的宽度。如图3.10d所示。(7) 重叠电源与地线层规则。不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。如图3.10e所示。(8) 尽量选择表面贴装器件,并尽量选择小尺寸元件。由于SMD器件引线的互连长度很短,因此引线的电感、电容和电阻比DIP器件小得多。(9) 综合运用接地、屏蔽和滤波等措施。

3.11 PCB的抗ESD设计

随着IC采用更先进的工艺技术进行制造,其变得更容易受到ESD的伤害,而且随着数据传输速率的提高,必须同时提供好的信号完整性和ESD保护性能。因此电子产品的静电放电防护设计非常重要。通过PCB的分层设计、合适的布局布线和安装等可以实现PCB的抗ESD设计。(1) 尽可能使用多层PCB。相对于双面PCB,地平面和电源平面以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10~1/100。尽量地将每一个信号层都紧靠一个电源层或地线层,对于顶层和底层表面都有元器件、具有很短连接线以及许多填充地的高密度PCB,可以考虑使用内层线。(2) 对于双面PCB来说,要采用紧密交织的电源和地栅格。电源线紧靠地线,在垂直和水平线或填充区之间,要尽可能多地连接。一面的栅格尺寸≤60mm,如果可能,栅格尺寸应<13mm。(3) 确保每一个电路尽可能紧凑,尽可能将所有连接器都放在一边。(4) 要以下列方式在电路周围设置一个环形地:除边缘连接器以及机壳地以外,在整个外围四周放上环形地通路;确保所有层的环形地宽度大于2.5mm;每隔13mm用过孔将环形地连接起来;将环形地与多层电路的公共地连接到一起。(5) 在能被ESD直接击中的区域,每一个信号线附近都要布一条地线。(6) I/O电路要尽可能靠近对应的连接器。(7) 对易受ESD影响的电路,应该放在靠近电路中心的区域,这样其它的电路可以为它们提供一定的屏蔽作用。 (8) 通常在接收端放置串联的电阻和磁珠,在连接器处或者离接收电路25mm的范围内,要放置滤波电容。在距离每一个连接器80mm范围以内放置一个高频旁路电容。(9)要确保信号线尽可能短。信号线的长度大于300mm时,一定要平行布一条地线。(10) 确保信号线和相应回路之间的环路面积尽可能小。对于长信号线,每隔几厘米调换信号线和地线的位置来减小环路面积。(11) 确保电源和地之间的环路面积尽可能小,在靠近集成电路芯片每一个电源管脚的地方放置一个高频电容。(12) 尽量要用地填充未使用的区域,每隔60mm距离将所有层的填充地连接起来。确保在任意大的地填充区(大约大于25×6mm)的两个相反端点位置处要与地连接。(13) 电源或地平面上开口长度超过8mm时,要用窄的线将开口的两侧连接起来。(14) 复位线、中断信号线或者边沿触发信号线不能布置在靠近PCB边沿的地方。(15) 将安装孔同电路地连接在一起,或者将它们隔离开来。在安装孔顶层和底层上要采用大焊盘。(16) 不能将受保护的信号线和不受保护的信号线并行排列。(17) 要特别注意复位、中断和控制信号线的布线。要采用高频滤波;远离输入和输出电路;要远离电路板边缘;(18) 要注意磁珠下、焊盘之间、可能接触到磁珠的信号线的布线。有些磁珠导电性能相当好,可能会产生意外的导电路径。

3.12 PCB焊盘设计

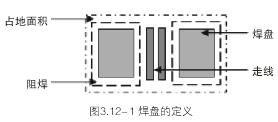

焊盘设计对SMT产品的可制造性、可靠性等有着很大的影响,是PCB设计中非常重要的部分。良好的焊盘设计能避免出现虚焊、短路、立碑、阴影效应等问题。IPC提供了表面贴装设计与焊盘结构标准——IPC-SM-782A,2005年IPC发布了IPC-SM-782A的替代标准IPC-7351。因为影响焊盘尺寸的因素众多,必须全面的考虑才能做好,应该根据实际情况做出适合自己产品的PCB焊盘设计规范,而不能完全依靠IPC标准。焊盘设计的一般考虑顺序为:保证良好的电气性能;可靠性;可制造性;可维修性。焊盘设计需要确定的要素,包括焊盘本身的尺寸、绿油或阻焊窗尺寸、元件占地范围、元件下的布线或粘胶用的虚设焊盘等。如图3.12-1所示:

决定焊盘尺寸的主要因素有五方面:元件的外形和尺寸、基板种类和质量、组装设备能力、所采用的工艺种类和能力、要求的品质水平或标准。在考虑焊盘的设计时必须配合以上五个因素整体考虑。计算尺寸公差时,业界中较常用的是统计学中接受的有效值或均方根方法,这种做法能在各方面达到较好的平衡。一个良好的焊盘设计,应该提供在工艺上容易组装、便于检查和测试、以及组装后的焊点使用寿命长等条件。保证良好的焊盘设计的条件:(1)建立元件封装资料档案;(2)对每一个SMD建立器件的封装尺寸库;(3)确定不同供应商的尺寸误差;(4)建立基板规范;(5)制定厂内工艺和设备能力规范;(6)对各制造工艺的问题和知识有足够的了解;(7)制定厂内或对某一产品上的品质标准。

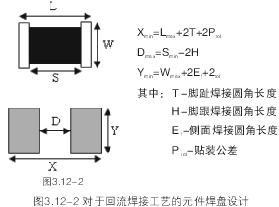

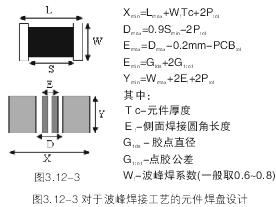

矩形片式元件焊盘设计(见图3.12-2~3.12-3):

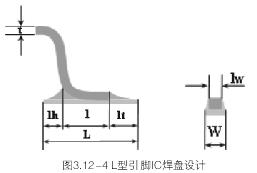

L型引脚IC焊盘设计(见图3.12-4):

(1) 适应范围:在SOT、SOIC、(S/T)SOP、(P/S/-C)QFP等封装的引线。(2) 参数说明:t:引脚厚度(lead thickness)典型值为0.1~0.15mml:引脚长度(lead length) 典型值为0.6~0.8mmlw:引脚宽度(lead width) W:焊盘宽度(pad width) L:焊盘长度(pad length)lh:引脚跟部长度(lead heel) 通常为0.5mmlt:引脚前端长度(lead tip) 通常为0.5mm(3) 焊盘尺寸设计:焊盘长度:L=lh+l+lt 通常为1.5~1.8mm焊盘宽度:W=lw+2millh=lt= =(2.6~5.6)t 其中θ=15o~30oJ型引脚IC焊盘设计(见图3.12-5):

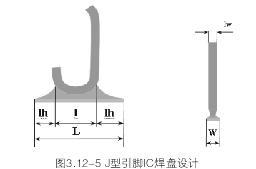

(1) 适应范围:SOJ、PLCC等部品的封装引线。(2) 参数说明:l:引脚长度(lead length)B:引脚宽度(lead width)W:焊盘宽度(pad width)L:焊盘长度(pad length)lh:引脚跟部长度(lead heel)(3) 焊盘尺寸设计:引脚跟部长度:lh=T/2焊盘长度:L= 2lh+l 焊盘宽度:W=lw+ lwBGA焊盘设计(见图3.12-6):

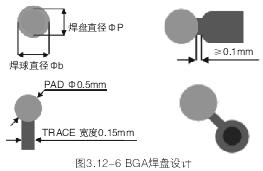

(1) 焊盘直径按照焊球直径的75%~85%设计。(2) 焊盘引出线不超过焊盘的50%,相对于焊接质量来说,越细越好。(3) 电源焊盘的引出线不小于0.1mm,方可加粗。(4) 为了防止焊盘变形,阻焊开窗(solder mask) 不大于0.05mm。

四、总结

PCB的优化设计在产品开发设计过程中有着重要的作用,每个设计人员都应该认真考虑,确保产品设计的最优化,使产品朝着“无缺陷”或“零缺陷”的方向发展。

文章摘自《印制电路资讯》09年3月第二期

本文资料经作者授权:PCB网城版权所有,转载请注明出处,抄袭必究。

关于powerpcb就介绍完了,您有什么想法可以联系小编。