今天小编要和大家分享的是布线技巧与EMC相关信息,接下来我将从便携式设备高速端口的ESD防护,max512esd这几个方面来介绍。

布线技巧与EMC相关技术文章便携式设备高速端口的ESD防护

便携式设备高速端口的ESD防护

在高速数据率下,低电容ESD保护对于保持USB2.0,IEEE1394以及ITV操作中使用的DVI和HDMI协议的数据完整性是很关键的。

全世界有数百万的家庭都已经在通过卫星电视、有线电视以及陆地广播享用互动式电视(ITV)服务。借助于计算机技术,ATSC ACAP协议正在通过数据广播(PC下载)以及实时互动应用服务成为富有生命力的广播服务。通过将计算机装入电视机并为数字式机顶盒增加游戏、运动、互动广告、电子信箱和因特网接入功能,ITV正在成为电视和家庭娱乐的一道风景线。

ESD抑制器件保护数据传输线路保持信号完整性

随着这些行业的汇聚联合,制造商必须对设备需求做出响应,以便容纳更高的数据率以及符合当前和拟议中的通信需求。另外,保护昂贵的设备不会受到因用户错误操作、环境危害或电源变化所引起的致命的损坏也是一项关键的设计课题。 USB 2.0、IEEE1394、ITV应用和操作中使用的数字式可视接口(DVI)和高清晰度多媒体接口(HDMI)协议允许高速数据传输率,并可以支持即插即用热插拔安装和操作。但这些外部端口很容易受到来自工作环境和周边设备的破坏性的ESD脉冲的伤害。ESD抑制器件除了保护数据传输线路之外,必须保持其信号的完整性。

通常,USB 2.0支持480Mbps(bits per second)的数据传输;DVI和HDMI协议更是分别支持高达8Gbps和5Gbps的数据传输带宽。在USB2.0、DVI和HDMI的高速数据率下,传统保护装置的寄生电容可能破坏信号的完整性或令其失真。失真表现为由较慢的上升和下降时间所致的高态/低态瞬变的前沿和后沿被修圆。上升和下降时间较慢会给系统带来一些问题,其中最重要的是时序问题。电路在特定的时间需要稳定的"高"态和"低"态。随着各状态之间过渡时间的增加,电路有可能检测到不完整的过渡期,从而将数据误差引入系统。附表1是不同寄生电容ESD抑制器件对数据上升沿时间(10%至90%高电平)所造成的影响比较。

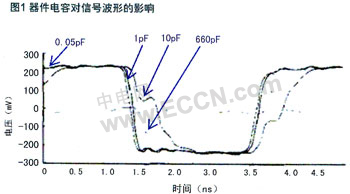

传输速率为12Mbps时,其保持电平的时间要长得多(80ns)。在此数据传输率条件下,10pF或更小的电容值将使得数据通过时的失真最小。当传输速率提高到480Mbps时,信号具有短得多的电平保持时间(2.0ns)。此时10pF电容的ESD抑制器件已经引起波形失真:它减少了电平保持时间并使前沿和后沿的形状大为改变。而660 pF电容的ESD抑制器件则造成了相当大的失真,以致于波形甚至无法达到信号工作电压。图1显示了不同ESD抑制器件对480Mbps数据波形的影响。

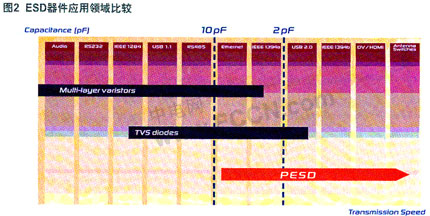

这些数据揭示了在进行超高速系统的数据传输线路保护时ESD抑制器的电容特性的重要性。尽管现有的各种抑制器均能够提供有效的ESD保护功能,但不能以牺牲系统的信号完整性为代价。因此,在把ESD抑制器引入电路设计之前,必须对其电容有所考虑。具有极低电容值的ESD抑制元件(如PESD器件)能够在提供ESD保护功能的同时保持高速数据信号的数据完整性。由于传输最高速率的不同,不同的数据接口所能接受的最高电容是不一样的。譬如,USB2.0数据线上的寄生电容一般控制在10pF以内,而DVI或HDMI数据接口要求则更低,通常低于1pF(图2)。

高速信号和瞬变(如ESD)还带来了另一个寄生特性--电感。尤其值得关注的是用来实现连接器、芯片及其他任何配套元件之间互连的电路板上迹线的寄生电感。与电容效应相似,由电路板迹线所产生的电感将不会影响低频信号。但是,任高速条件下,这种电感将产生有可能影响信号完整性的阻抗分量。当高频信号(如ESD)通过时,少量的迹线电感可能转换成巨大的阻抗。设计师可通过在ESD抑制器和受保护芯片之间设置尽可能大的距离的方法来利用上述特性来完善ESD器件和IC本身间的协同、偶合。

低电容ESD保护对于高速条件下保持数据的完整性是非常关键的。在常见的瞬间过电压抑制器件中,金属氧化物压敏电阻(MOV)和多层压敏电阻(MLV)因价廉物美而应用广泛。但其固有的高电容决定了其应用范围只能局限于低频领域和电源的瞬间电压抑制上。而硅类ESD防护器件,包括齐纳二极管、TVS二极管/阵列等,虽然具有保护电压低而准确的优点,其寄生电容依旧不可忽视,通常难以适用于高速数据通讯接口,如HDMI、IEEE1394等。

ESD防护的应用

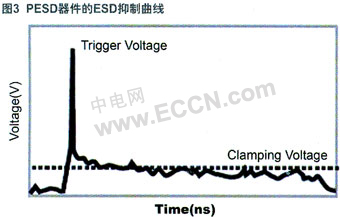

为满足高速数据通讯接口既ESD保护有效、又不影响高速信号传输的要求。近年来,市场上推出了多种专门适用于此类保护要求的器件。其中以瑞侃电路保护部门(RCP:RaychemCircuit Protection)推出的PESD器件为代表。该器件的电容极低(通常0.25pF),漏电流极小(<0.001 A);ESD防护快速有效(响应曲线如图3所示,触发电压典型值为150~250V;响应时间少于1 ns);价格低于低电容硅器件。因此,在高速数据传输条件下,PESD器件拥有更佳的保护应用特性。该器件已成功应用于HDMI1.3和USB2.0等多种高速接口电路。

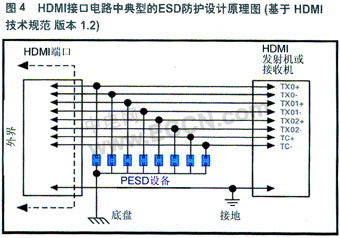

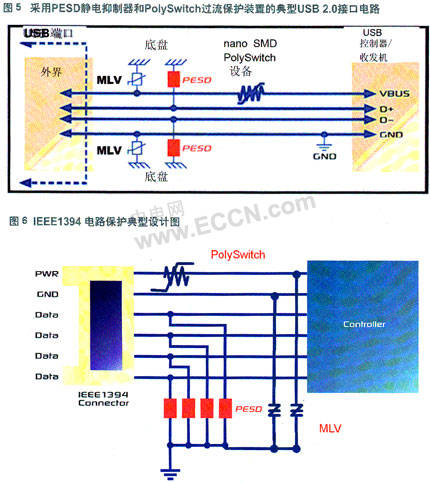

图4、图5和图6展示了利用瑞侃电路保护部门PESD器件对HDMI1.3、USB2.0和IEEE1394接口电路进行保护的典型应用。这些保护将ESD与敏感电路隔离。在传输线路脉冲(TLP) 测试和IEC61000-4-2测试中,尤其是经过多次采样(1000次TLP测试)后,其性能要比其他可比较的元件好。相对于其他典型的聚合物ESD防护器件,这类PESD器件的较低触发电压(通常150V)和低箝位电压(通常25V)能更好的帮助保护敏感电子元件。该器件采用电子工业中最流行的0603和0402贴装形式,符合RoHS的严格要求;帮助机顶盒敏感电路、手提电脑、手机和其它便携式设备免ESD侵害。

优化ESD保护

当选择了一个抑制和电特性(漏电流、电容)与电路参数相吻合的ESD抑制器之后(如PESD),还需要作出另一项选择:抑制器应安装在电路板的什么位置上才能优化电路的ESD保护?"优化"ESD保护指的是使受保护芯片上的ESD瞬变尽可能少。简单地讲,应把ESD抑制器直接放置在连接器的后面。它应该是第一个遭遇ESD瞬变的板级元件。然后,在实际可行的情况下,任何需要保护的芯片均应尽可能地远离ESD抑制器。采取这一方法将极大地减轻集成电路所承受的应力。下面列出的是PESD器件安装位置的相对优先级,按从高到低的顺序排列如下:

* 设置于作为系统屏蔽(机壳)中的入口的连接器的内部

* 安放于电路板迹线与连接器插脚相互作用的位置

* 放置于电路板上紧挨在连接器后面的位置

* 位于可以高效耦合至I/O线路的性能稳定且未受保护的传输线路

* 设置于数据传输线路上的一个串联阻性元件之前

* 位于数据传输线路上的一个分支点之前

* 靠近IC和/或ASI

另一个需要考虑的布局问题是从PESD到被保护IC的距离和偶合电阻的选择。目标是将该距离降至最小。需要保护的IC通常自身带有ESD保护。但这只属于器件级的防护,且致性较差,需要PESD器件协助/偶合达到设备/系统级的ESD防护。随着与传输线路之间距离的增加,ESD抑制器变得越发与受其保护的信号线"隔离"开来。与电路板走线相关联的电感以及任何的封装寄生电感都将在保护电路中加入阻抗,成为PESD电压抑制器和IC间的偶合阻抗。因为IC芯片将要承受抑制器两端和偶合阻抗两端的电压之和,理想的设计应使PESD尽可能多承受应力,同时保证两级防护间没有遗漏的"死角"。

最后,机壳(框架)的地应是ESD基准,而不是信号(数字)地。目的是把ESD从信号环境中屏蔽出去。使ESD TVS保护器件以机壳的地为基准,则可免受那些不希望的噪声效应(如接地反跳)的影响。日标是尽量保持"干净"的信号(数据)环境。

关于布线技巧与EMC就介绍完了,您有什么想法可以联系小编。