今天小编要和大家分享的是Altium Designer,Protel相关信息,接下来我将从航空电子系统设计中FPGA技术的应用,赛灵思ultrascale架构 - fpga/asic技术 - 电子发烧友这几个方面来介绍。

Altium Designer,Protel相关技术文章航空电子系统设计中FPGA技术的应用

航空电子系统设计中FPGA技术的应用

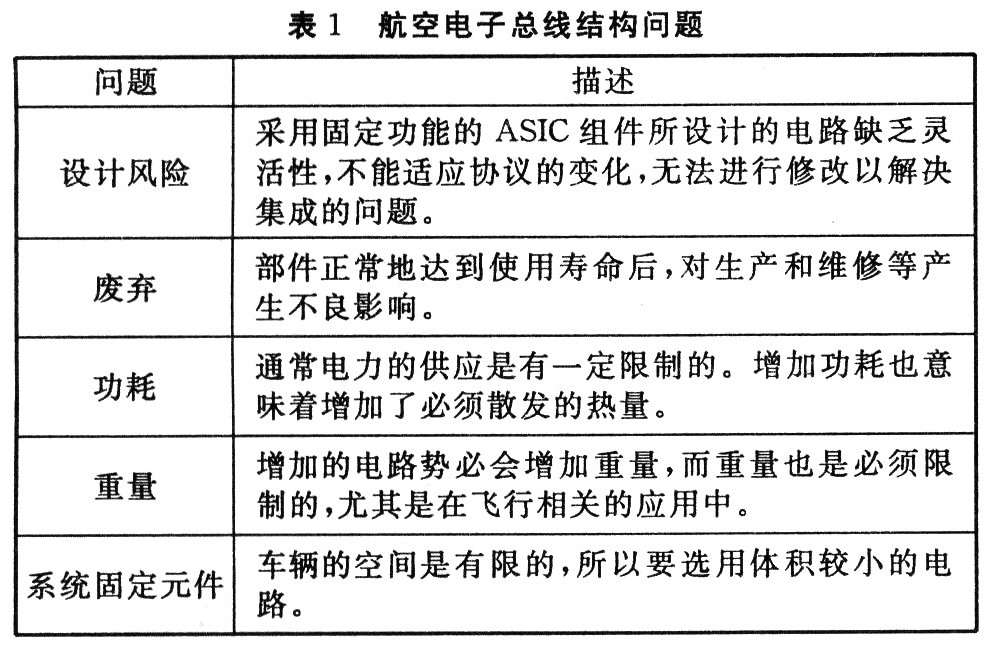

1 系统设计面临的问题 由于竞争的压力和对飞机性能无止境的追求,航空电子从简单、独立的设备发展到如今以每秒百万位乃至更快的速度交换信息的高级智能系统网络。这也带来了必须克服的许多设计问题(见表1)。

在要求高性能的航空系统设计中,每项设计都要减少空间、功耗和重量,满足这些要求至关重要。这项要求直接作用于芯片级别,单一芯片体积减小后对所需板卡的要求也会降低,从而降低了对封装外壳、固定元件、冷却器件甚至是电源的要求。同样,每多增加一个组件,都会增加一些引发故障的机会。减少芯片数量的设计必然有助于缓解这些问题。废弃则是像MIL-STD-1553设计实施这类长期项目所面临的另一个问题。每个组件无论其是由世界最大的制造商提供,还是来自于产量较小的专业供应商,都存在着废弃的风险。单一来源的组件不但面临着被废弃的风险,还有个长期价格保护的问题,特别是那些从原有项目继承的设计,这个问题更为明显。对于已经部署的系统,由于所涉及的代价过高,应尽量避免由于废弃组件而重新对系统进行验证。当系统架构师指定一种系统设计时,必然会存在架构无法正确实现的某种风险。一个非常典型的问题是:经常在设计过程中或架构确定很久之后(如在集成阶段),才知道需求有所变化。这些变化一般都会增加对架构的要求,并提出一些关于设计的常见问题,如:设计足够灵活吗?能提供充分的处理能力吗?功能在硬件和软件之问是否得以有效且高效地进行了区分?能达到关键时间要求吗? 理想状况下,所选定的架构应功能强大、应用灵活,足以在初始部署阶段就将风险降到最低,并且提供了一个允许系统随着时间发展的平台。 理想条件下,一个MIL-STD-1553设计师可以采用传统的技术,使用有多个来源的COTS组件来解决这些问题。这种由大量市场提供的组件在性价比上有明显的优势。

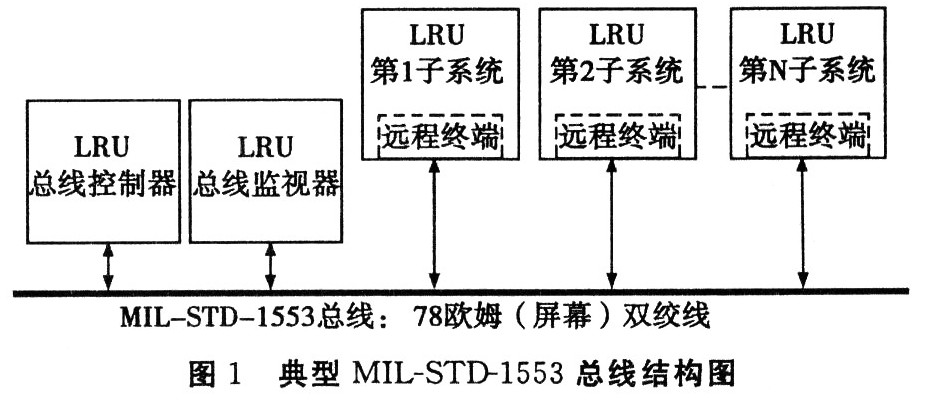

2 MIL-STD-1553简介 请看一下数据传输路径,即图1中的MIL-STD-1553总线结构。MIL-STD-1553是一种定义数据总线的电子和协议特点的军用标准。作为一种在军用和商用领域广泛应用超过25年之久的总线,并且符合MIL-STD-1553标准,它能以1 Mbit/s的速率高度精确、极为可靠地传输数据。

根据MIL-STD-1553标准的规定,总线结构由三个不同的硬件组成: ●总线控制器——总线控制器是总线上唯一允许在数据总线上发出命令,并负责引导数据总线中数据流的硬件设备。如果同时有几个终端可以实现总线控制器的功能,同一时间内只能有一个处于活动状态。

●总线监视器——总线监视器是一个可以监控总线上信息交换的终端。它可以用于飞行测试记录、飞行故障诊断、维护记录与任务分析,同时还可作为一个备用总线控制器,它有足够的信息可以接替总线控制器。然而,总线监视器是一个被动的设备,它不能报告所传输信息的状态。 ●远程终端——每个远程终端都包括在数据总线和子系统间传输数据所必须的电子器件和支持性中间件。对于MIL-STD-1553,子系统就是所传输数据的发送者和接收者。这些终端不能作为总线控制器或总线监视器使用。

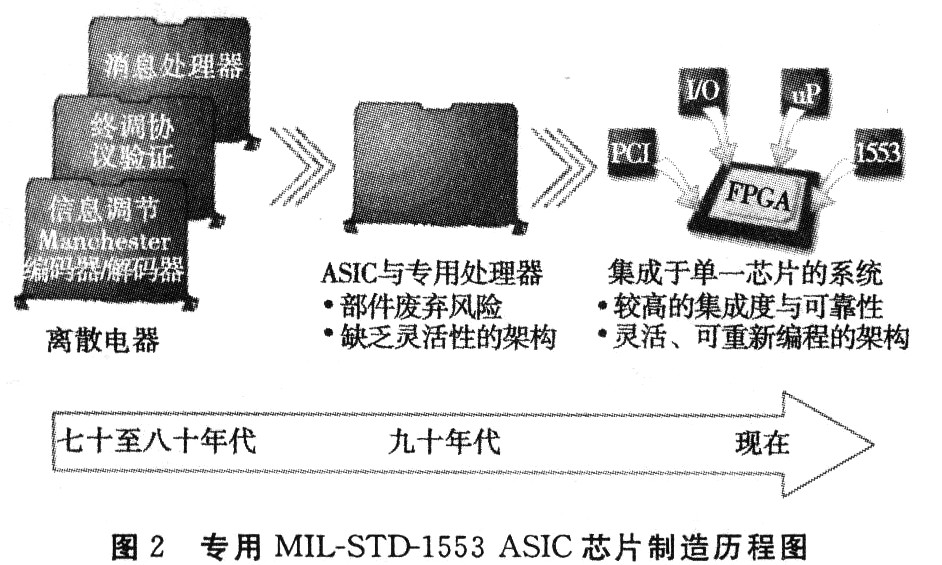

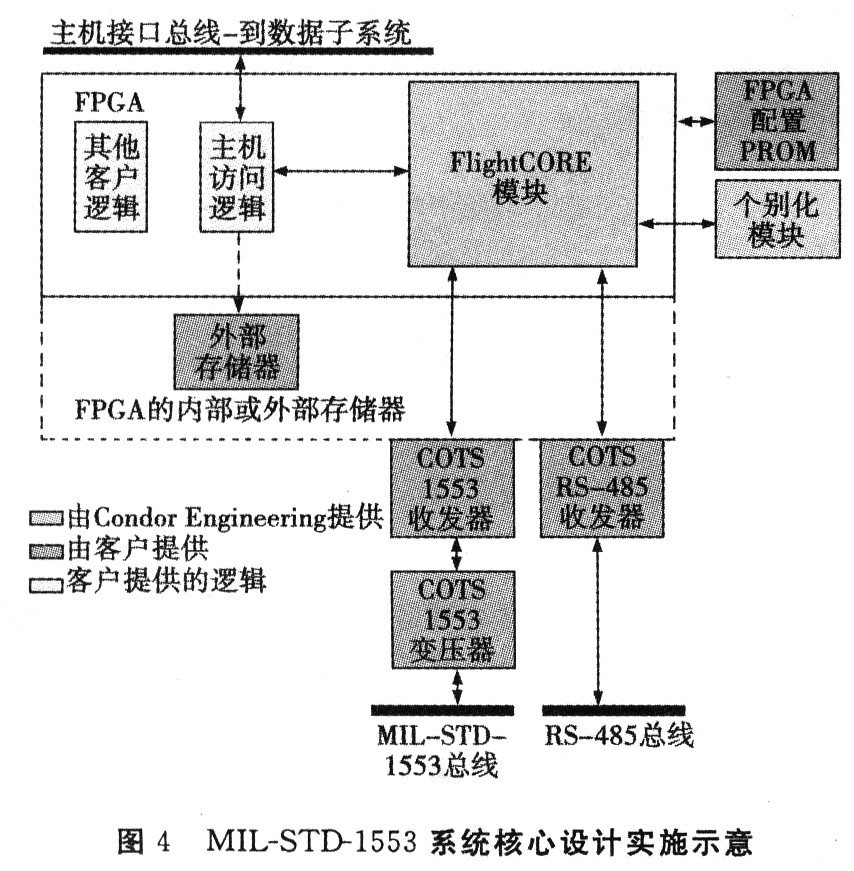

3 MIL-STD-1553系统实施 像其它网络技术一样,航空电子市场中的MIL-STD-1.553测试和仿真实施也经历了从庞大的DEC Unibus卡到19英寸的通过机架安装的组件,又发展到用于VME和PCI系统上的较小、较为集成的多通道背板,现在又出现了更小、集成度更高的。 PCMCIA接口。图2描述了专用的MIL-STD-1553 ASIC芯片制造商的实施从离散的协议和收发器芯片组精简到单一的体积小、功耗低的ASIC的发展过程。

(4)便于重新编程——由于支持对现场硬件的重新编程,核心的实施显著降低了设计风险。如果系统需求发生变化,或者要修复一个错误时,基于FPGA的设计可以在软件的控制下进行升级。这种灵活性还可以在硬件构造完成后,在硬件和软件间重新区分功能。例如,如果在集成阶段发现软件不能有效地响应一个实时事件,可以将该功能下移到FPGA级别,这样就将原由软件实现的功能转化为硬件功能。

●总线监视器——总线监视器是一个可以监控总线上信息交换的终端。它可以用于飞行测试记录、飞行故障诊断、维护记录与任务分析,同时还可作为一个备用总线控制器,它有足够的信息可以接替总线控制器。然而,总线监视器是一个被动的设备,它不能报告所传输信息的状态。 ●远程终端——每个远程终端都包括在数据总线和子系统间传输数据所必须的电子器件和支持性中间件。对于MIL-STD-1553,子系统就是所传输数据的发送者和接收者。这些终端不能作为总线控制器或总线监视器使用。

3 MIL-STD-1553系统实施 像其它网络技术一样,航空电子市场中的MIL-STD-1.553测试和仿真实施也经历了从庞大的DEC Unibus卡到19英寸的通过机架安装的组件,又发展到用于VME和PCI系统上的较小、较为集成的多通道背板,现在又出现了更小、集成度更高的。 PCMCIA接口。图2描述了专用的MIL-STD-1553 ASIC芯片制造商的实施从离散的协议和收发器芯片组精简到单一的体积小、功耗低的ASIC的发展过程。

(4)便于重新编程——由于支持对现场硬件的重新编程,核心的实施显著降低了设计风险。如果系统需求发生变化,或者要修复一个错误时,基于FPGA的设计可以在软件的控制下进行升级。这种灵活性还可以在硬件构造完成后,在硬件和软件间重新区分功能。例如,如果在集成阶段发现软件不能有效地响应一个实时事件,可以将该功能下移到FPGA级别,这样就将原由软件实现的功能转化为硬件功能。

(5)适应多种机体——灵活,可重新编程的解决方案适于为多种机体构架或针对多用途基础设计的飞航测试线上可更换件(LRU)。由于USAF和NATO的多种机体采用从MIL-STD-1553B标准分离出来的协议,所以多种机体的LRU需要灵活、可编程的设计。某些设计实施了通过特殊的子地址或模式代码协议进行寻址扩展的数据集。很多固定翼和可旋转翼飞机同时采用了较老的MIL-STD-1553A和MIL-STD-1553B LRU,这就要求总线控制器和总线监视器能够处理不同的协议。

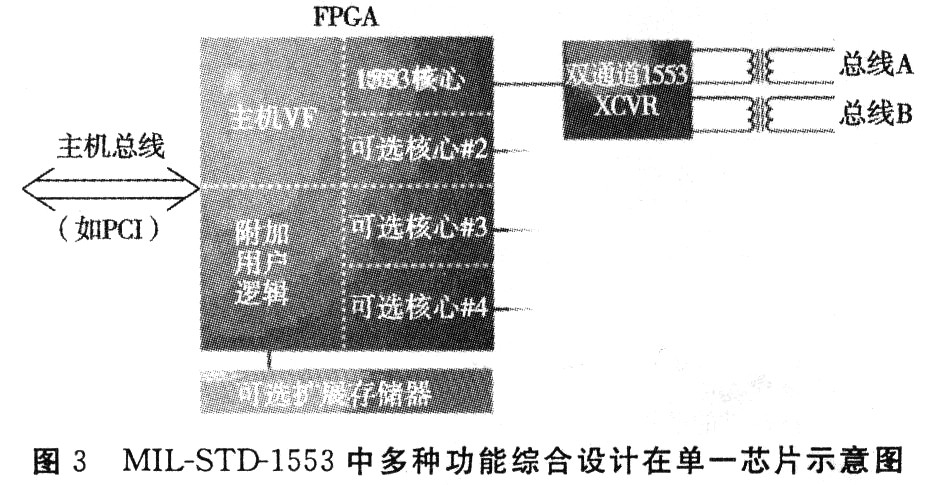

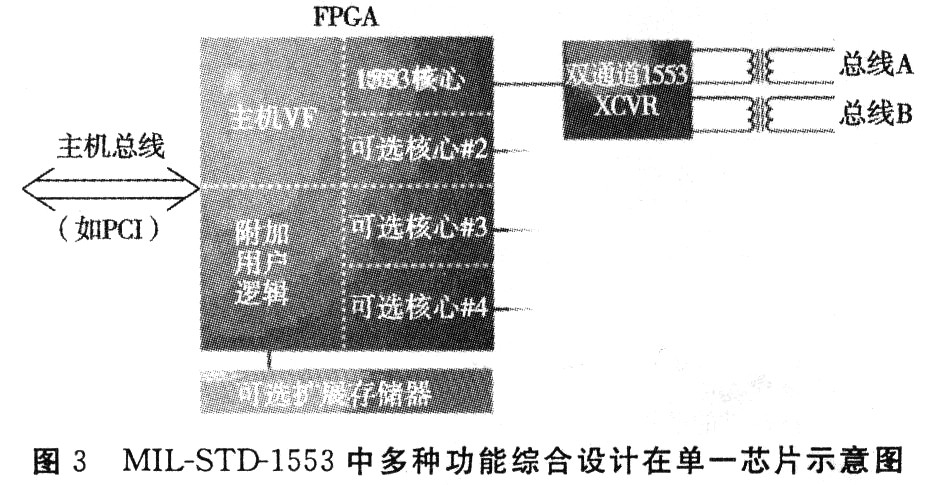

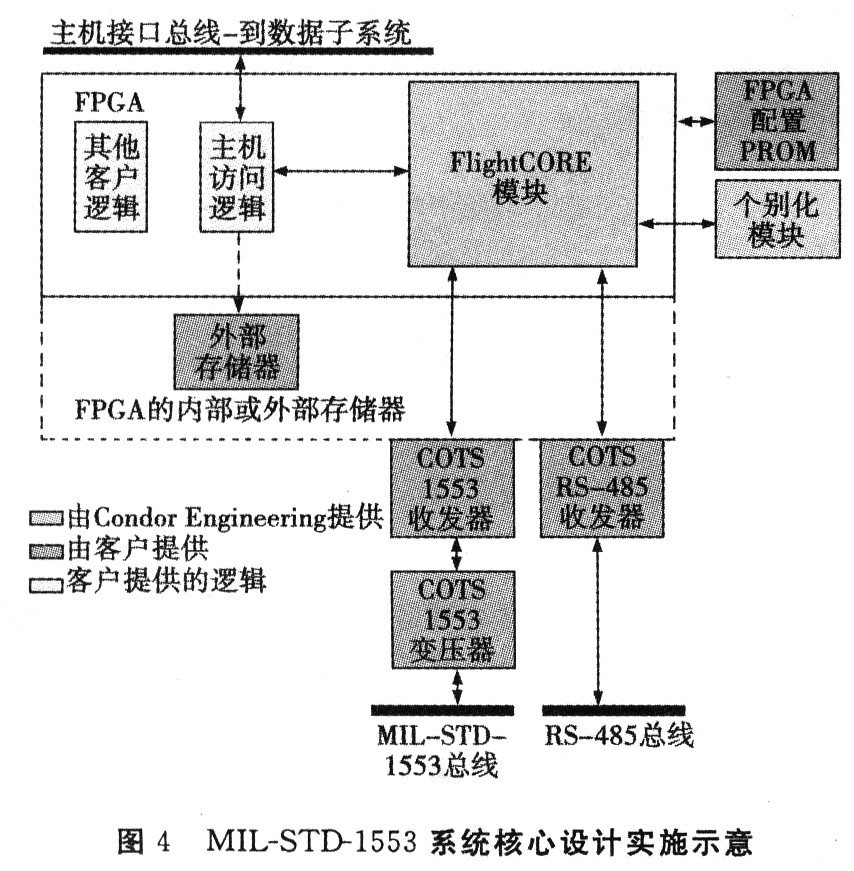

4 对MIL-STD-1553系统设计采用基于核心的实施 现代FPGA的强大功能使其成为MIL-STD -1553设计的理想选择,这就是Condor Engineering推出FlightCORE的原因。FlightCORE是一种允许设计人员在各种Altera和Xilinx的FPGA中轻松实现无版权的实例化设计的MIL-STD-1553 IP。多数情况下,利用Xilinx综合技术(XST)或Altera Quartus II集成综合技术(QIS),FlightCORE 1553可以在两天内成功地集成。如图4所示,用户只须将CondorEngineering的IP核心与其自身逻辑和Condor Engineering的个别化模块(3 mm×3 mm)集成,即可实现高性能的MIL-STD-1553设计。FlightCORE还允许开发人员选择存储器的大小以恰好地与其系统需求相匹配。图4还显示了可以实施内部存贮和/或外部双端口随机存贮器。该产品还提供了Manchester II编码与解码、信息协议验证与合法化及为接口控制和编程实施简单的共享存贮架构等所有的必要组件。只需增加外部收发器即可,如标准的COTS MIL-STD-1553或RS-485收发器。

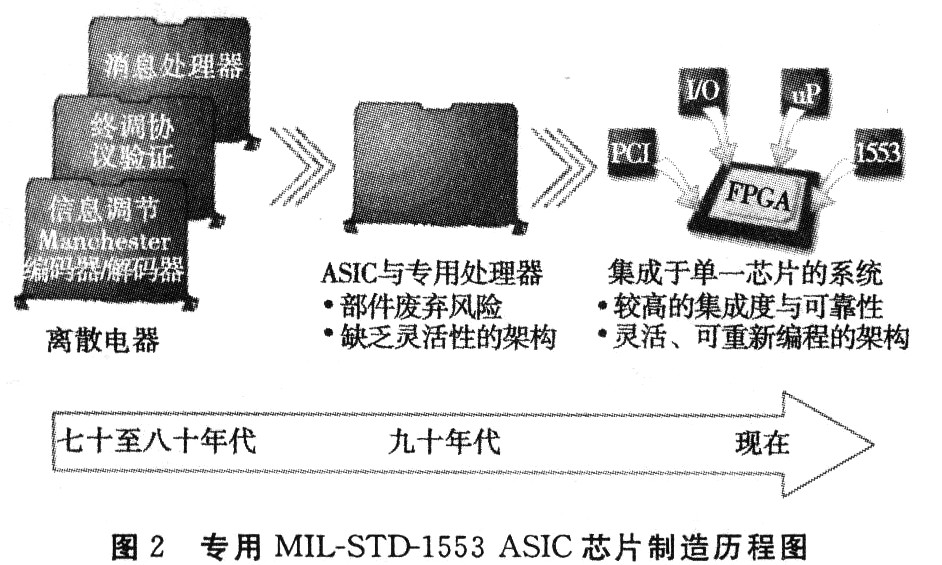

5 单一芯片上集中多个实例 类似Condor Engineering的FlightCORE这样的MIL-STD-1553解决方案需要少量的FPGA资源,约为3000个逻辑单元,148 kbit的内存和不到20个引脚(不包括外部主存总线)。较小的体积使在单一芯片上放置多个相互独立的实例成为可能,如图3所示,某些程序可以在单一 FPGA上集中8到10个实例。

6 结论 FPGA与其容纳的“知识产权”使设计人员可以对LRU进行修改或专门设计,以适应不同的航空电子通信和日新月异的升级之间的微小差异。像Condor Engineering的MIL-STD-1553、1.Mb和10 Mb的FlightCORE IP这样的通信核心,提供了一种直接而灵活的方法,可有效地解决日益增长的功能和废弃问题。

关于Altium Designer,Protel就介绍完了,您有什么想法可以联系小编。