隔离一块PCB板上的元器件有各种各样的边值(edge rates)和各种噪声差异。对改善SI最直接的方式就是依据器件的边值和灵敏度,通过PCB板上元器件的物理隔离来实现。

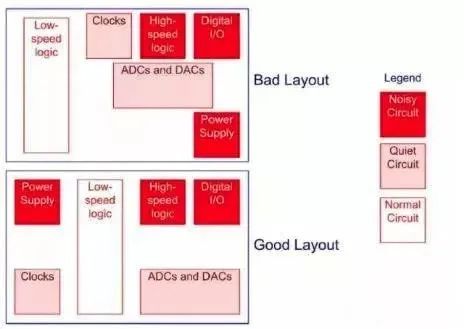

图1是一个实例。在例子中,供电电源、数字I/O端口和高速逻辑这些对时钟和数据转换电路的高危险电路将被特别考虑。

第一个布局中放置时钟和数据转换器在相邻于噪声器件的附近,噪声将会耦合到敏感电路及降低他们的性能。第二个布局做了有效的电路隔离将有利于系统设计的信号完整性。

阻抗、反射及终端匹配阻抗控制和终端匹配是高速电路设计中的基本问题。通常每个电路设计中射频电路均被认为是最重要的部分,然而一些比射频更高频率的数字电路设计反而忽视了阻抗和终端匹配。