信号源产生模块

该模块主要包括PCI总线接口、信号产生控制逻辑电路(FPGA)、DDS芯片以及相应的放大、滤波和衰减电路。上位机通过PCI总线访问FPGA中的寄存器,实现对各种工作模式的控制。其中FPGA选用的是Altera公司的EP1K50TC144。晶振除了提供板上各个模块工作所需时钟外,还提供给其他处理板作为外时钟。设计中采用的DDS是AD9854,片内的4~20倍的时钟乘法器可使内部工作频率达到300MHz,输出信号的频率可达100MHz。

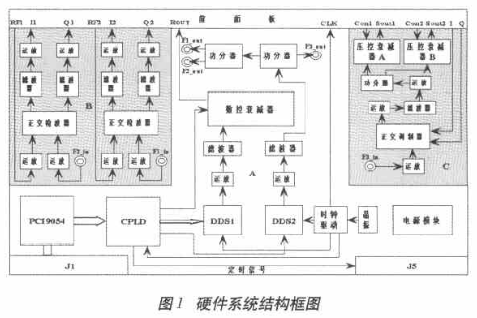

DDS的各种参数控制信号均由FPGA来提供,实现不同形式信号的输出。DDS1输出的chirp(线性调频)信号经过放大滤波后送入数控衰减器,然后进行波束调制,调制后的信号ROUT从前面板输出。DDS2输出的连续波信号经放大滤波后再经过两级功分器输出三个信号F1_out、F2_out和 F3_out,作为正交调制和检波模块的本振信号,通过板内的SMA与相应的模块连接。

正交检波模块

如图1中阴影部分所示,包括两路正交检波电路。被检波的中频信号RF1(RF2)由前面板送到板内,经过运放后输入正交检波器,本振信号由板内的SMA引入,即F1_in和F2_in,由模块A中功分器的输出F1_out和F2_out提供。经过正交检波器后输出I、Q信号,分别经滤波放大后输出,即得到需要的信号。