3、总体设计

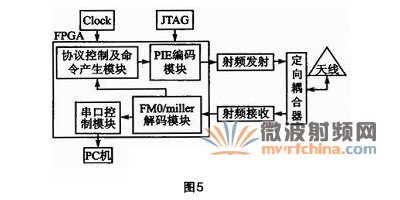

在本读写器设计中,ARM与FPGA协同工作。ARM芯片是LPC2148,工作时钟是20 MHz,主要完成对读写器系统的控制。而FPGA则负责编解码部分的数据流处理,工作时钟频率是25 MHz。图5是FPGA部分的整体设计框图。

图5 整体设计框图

FPGA中的模块主要包括协议控制及命令产生模块、PIE编码模块、FM0/miller解码模块,以及用于与PC机交互的串口控制模块。

工作过程如下:对读写器命令数据及其相应的CRC5/16校验位进行PIE编码,编码完成送到射频发射端,数字信号通过控制射频芯片RF2 173的开关引脚实现调制深度为100%的OOK(On-Off Keying)调制,并经由收发分离的定向耦合器,通过天线发射出去。

场内标签接收到读写器发送的信息后,在允许其通信的情况下,会根据读写器发送来的命令参数,选择4种编码方式中的一种,将要回复读写器的数据进行编码,经调制之后在空间传输。

读写器天线接收到标签信息后,经由定向耦合器将标签信息送到读写器的射频接收模块,该模块对标签信息进行解调,并将解调后得到的数字信号送给FPGA的FM0/miller解码模块。解码模块根据数据的编码方式选择相应的电路解码,解码后的数据返回给协议控制及命令产生模块。该模块根据上次发送的命令以及接收到的标签信息作出判断,产生下一次的操作命令数据,发给PIE编码模块,与该标签进行进一步的信息交互或选择重新读取另外的标签。