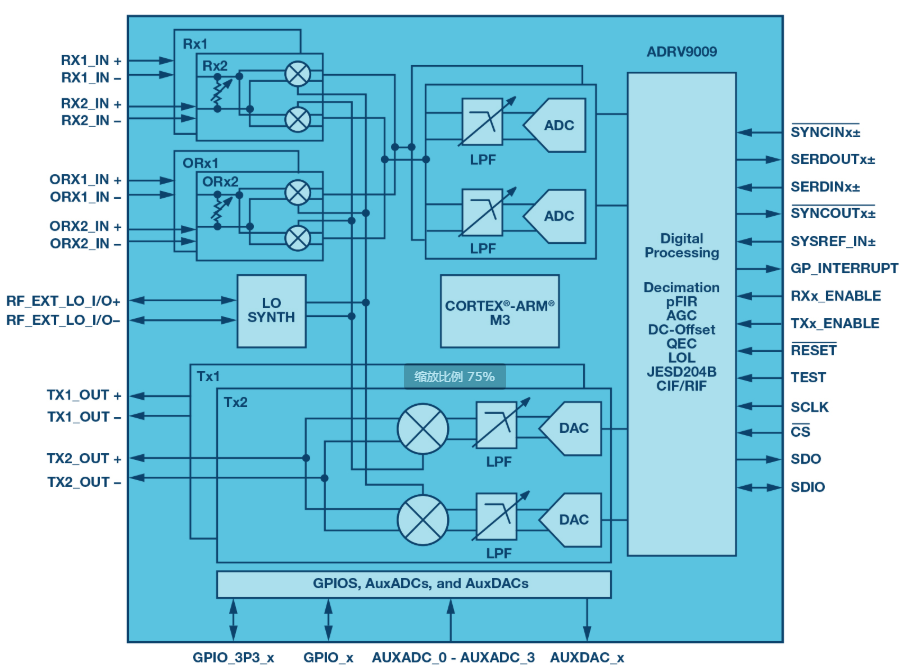

图1.ADRV9009是将多种功能集成到单个IC中的集成式收发器示例。

这些集成式收发器能够通过注入一个称为REF_CLK的参考时钟信号来创建发射器和接收器所需的所有时钟信号。然后,由片内锁相环(PLL)合成DAC/ADC采样、LO生成和微处理器时钟所需的所有时钟。如果内部LO相位噪声不足以满足客户的应用需求,用户可以选择注入自己的低相位噪声外部LO。

来自部件的数据经由标准化的JESD204b多千兆串行数据接口进行卸载。这个接口支持同时接收和传输大量数据。新集成式收发器解决方案可以帮助提供接口IP,帮助客户加快上市时间。如果需要确定性延迟和数据同步,用户可以利用内置的多芯片同步(MCS)特性,并发出SYS_REF信号作为初始通道对齐序列(ILAS)的主时序基准。1

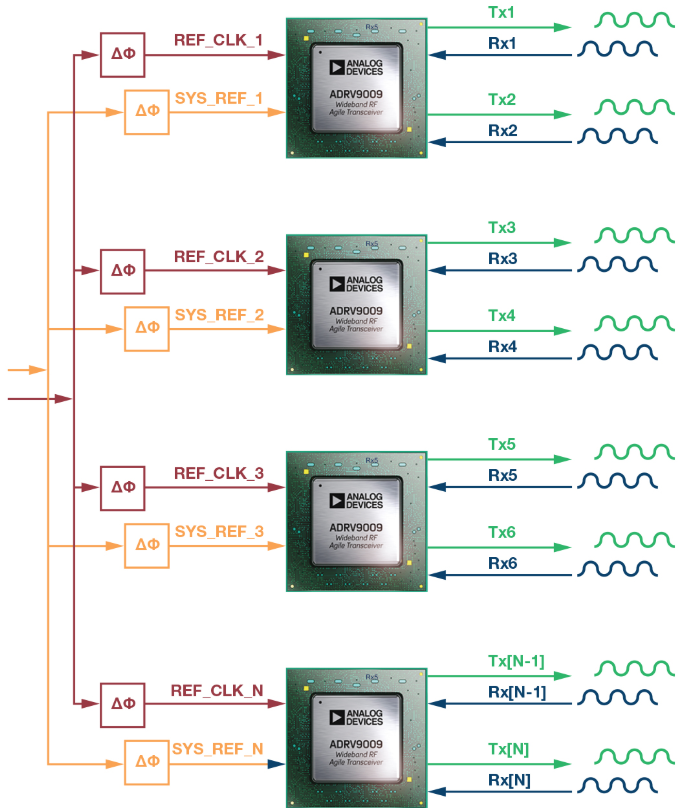

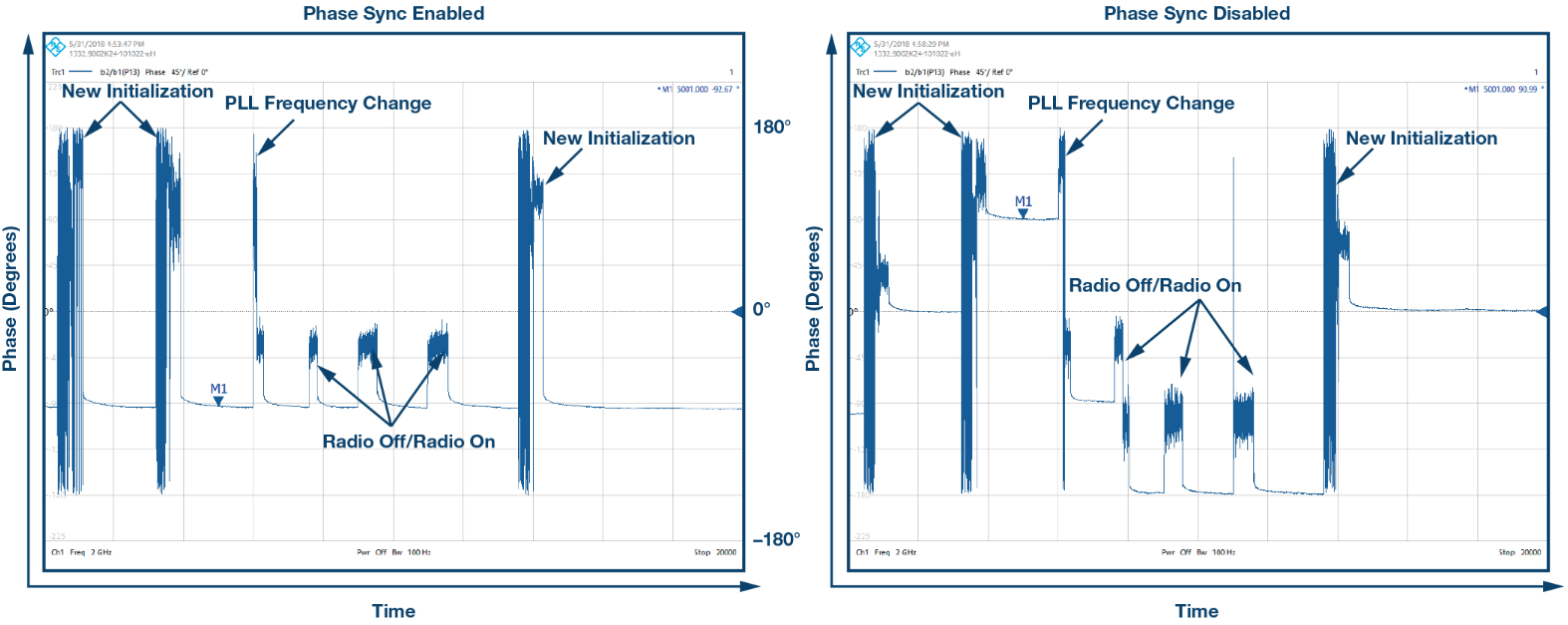

此外,可以利用内置的RFPLL相位同步特性,将发射或接收通道的LO相位设置为相对于主参考相位具备确定性。通过利用MCS和RFPLL相位同步特性,可以在初始化部件、频率调谐,或者开关软件上的无线电时复制相位对齐。图2显示了一个新型集成式收发器示例,该收发器提供决定性相位,且支持所有这些特性。

图2.内置RFPLL相位同步特性让系统与主参考源之间呈确定性相位关系。