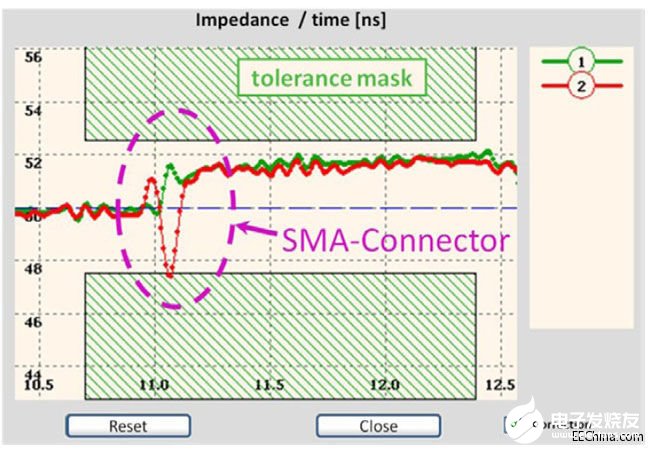

图3呈现的是RG 405同轴电缆的反射图,其中的同轴电缆分别按照组装规范(1)和没有按照组装规范(2)装配了SMA连接器。两种RG 405电缆的线路阻抗Z0≈51.5Ω,连接器区域的过渡非常明显。在错误安装连接器的情况下,电容下降(朝低阻抗变形)是可见的。当外部和内部导体安装靠得太近时这种效应会频繁发生(也就是构建了一个电容)。

图3:正确安装SMA连接器(1,绿)和错误安装SMA连接器(2,红)时RG 405同轴电缆的反射图。

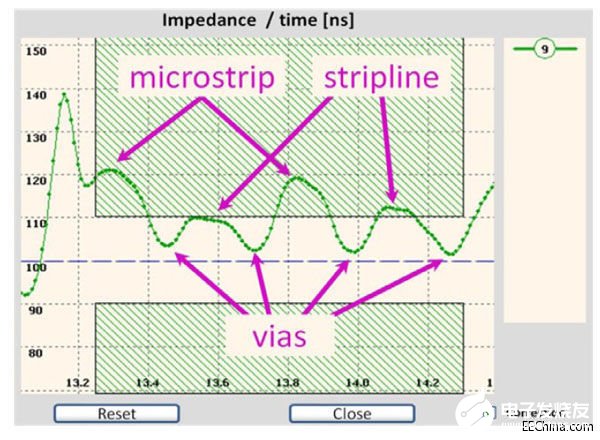

图4显示了4层印刷测试电路上的差分传输线的阻抗曲线。传输路径一开始是第一层(顶层)中的微带线,然后通过一个过孔转到第二层,此时仍然是微带线,再通过第二个过孔回到第一层表面。这个路线经过几次反复,最终在第一层终止。显然这个测试电路不能达到100Ω的目标阻抗:微带线和带状线的特征阻抗分别是Z0≈120Ω和Z0≈110Ω。从这张图中可以明显看出,过孔的电容因素会严重影响实际系统中的信号完整性,尤其是在高数据速率时更甚。

图4:在FR4基板的两个不同层上布线的差分线反射图。

作为最后一个例子,图5显示了USB 3.0连接器和电缆的反射图。USB 3.0组件的额定阻抗是Z0=90Ω±7Ω。TDR设备仍然工作在100Ω的参考阻抗上(时间范围t《12.2ns)。从测试适配器到USB 3.0连接器的转换引起的第一次反射发生在大约12.3ns,正如预期的那样与所有测量一致。曲线3(绿色)代表开放式适配器的结果,其中的快速阻抗上升指示适配器的(高阻抗)末端。曲线4和5(红色和蓝色)代表两种不同的USB 3.0电缆组件,每个组件由一个适配器和一个后续电缆组成。虽然电缆都在规范之内,但适配器不符合规范。特别是红色曲线表明最大阻抗约为122Ω,产生了严重反射,进而可能导致USB 3.0控制器降低数据速率。