3 数据采集卡电路设计

3.1 信号调理电路

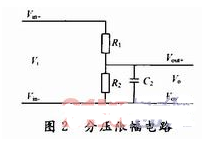

被测信号在进入A/D转换器之前,都必须进行适当的处理,使之符合A/D转换器的量程要求。对大信号需经过适当的衰减,而小信号则需要放大。本数据采集卡采用的A/D转换器的输入电压峰峰值在0~1 V之间,而被测信号幅度都大于此值,所以信号在进入A/D转换器之前需对其进行衰减处理。具体的分压限幅电路如图2所示。

3.2 A/D转换与FIFO缓存电路

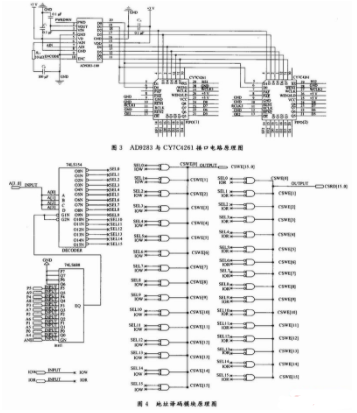

由于AD9283数据最大采集频率为100 MHz,所以其最大数据存储频率至少应为100 MHz,而CY7C4261的最大存储速率为100 MHz,能实现系统要求,系统中CY7C4261的写时钟与A/D转换采用同一个时钟进行控制。在测试过程中,有些待测信号周期较大,而本数据采集板的采样频率为100 MHz,为了在数据采集过程中不丢数据,需要连续采集大量数据。一片CY7C4261的存储容量不够,需要两片轮流存储。AD9283与CY7C4261的接口电路连接如图3所示。

4 CPLD在数据采集卡中的应用

CPLD作为整个数据采集过程的控制核心,负责地址译码、多路开关选通、A/D转换启动、将转换结果写入FIFO以及两片FIFO之间的切换等一系列操作。它的三个功能模块分别为:地址译码模块、多路开关控制模块、A/D采样及FIFO控制模块。