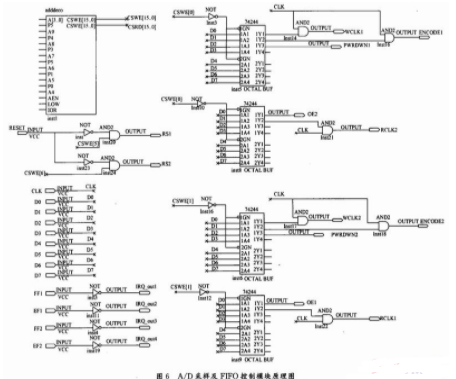

CPLD硬件控制逻辑设计的关键是分析各个器件的工作时序和采样保持时间,A/D转换时间以及数据存入FIFO的时间等。在设计的时序处理进程中,要根据CPLD的工作频率计算各个等待周期,等器件准备好以后才能进行下一个处理。

5 结语

采用CPLD和FIFO器件设计了一种基于PC/104总线的高速数据采集卡,它可以作为PC/104总线标准模件使用。该采集板上的大部分控制逻辑被集成到CPLD芯片中,大大减少了扩展卡上的器件数量,同时降低了系统成本,提高了系统的可靠性。该数据采集板非常适合搭建高密度、小体积的便携式测试设备,可广泛应用于武器控制系统的测试等多种场合,对控制系统的模拟量信号进行快速、实时的数据采集和分析。

责任编辑:gt

关于测量仪表就介绍完了,您有什么想法可以联系小编。