2.2 PCl-5640R程序设计

2.2.1 设计思想

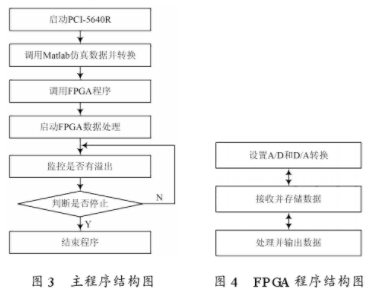

总的程序分圭程序设计和FPGA程序设计两块,主程序负责将数据读取、转换,然后送入FPGA,FPGA程序负责在FPGA上设计存储器,存储数据,并将数括通过 D/A转换送出。将Matlab仿真的数据以文本艾件的形式存储,并通过LabVIEW中的路径控件将文件载入,读取数据,再通过LabVIEW编程将数据转换为适合送入PCl-5640R中频板中的FPGA模块,并经过上变频器AD9857输出的数据,进而送人FPGA中。由FPGA控制将数据送入AD9857,最终输出中频回波信号。软件设计分主程序设计和FPGA 程序设计,结构图分别如图3,图4所示。

图4中的三个模块分别是三个定时循环,它们在执行时并无先后顺序,各自按预定的时序循环。

2.2.2 程序设计

(1)主程序设计

主程序的设计思路是:首先启动 PCl-5640R板卡,然后调用仿真数据进行转换,再将数据送入FPGA程序中处理,并不间断地从FPGA读取数据,以监控是否有溢出,最后判断是否有错误,若有则中断程序,如无则继续监控是否有溢出和有无错误,程序如图5所示。

图5(a)是将仿真数据通过路径控件读入到主程序中,再转换为16位数,然后通过Host to FPGA. Write控件将数据送入FPGA程序中。图5(b)是先通过一个逻辑控件开始一个FPGA程序中的Case结构,该结构是用于数据读取,然后通过一个for循环监视Memory是否溢出和数据是否送出到AO0口,并判断是否停止,最后结束数据读取并使FPGA停止工作。