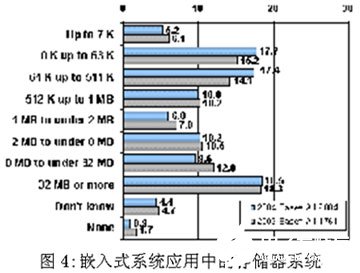

图4是EmbeddedSystemsProgramming和 EE Times在2004年度嵌入式市场调查中,所报告嵌入式系统使用存储器的情况。由图中的数据分布可看到与系统中所使用主处理器的情况极为吻合。工程师设计8bit和16bit处理器基系统时使用511k或更低的存储器。在设计32bit处理器基或FPGA基系统时使用32M或更高的存储器。

为查找这些大存储器故障,工程师需要有带宽高于500MHz的示波器。200MHz时钟将超出500MHz示波器的波形良好复现范围。按照老的经验法则,示波器带宽只有比所测信号的基频高4倍,才能保持波形的真实性。因此为精确测量200MHz时钟的当前SDRAM技术,工程师需要用800MHz带宽的示波器。

对持续采样速度的要求

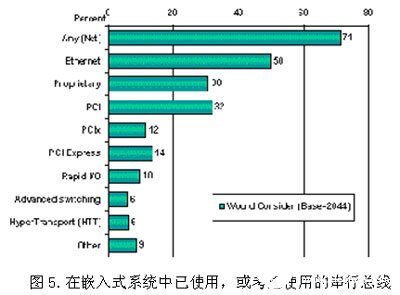

这些更高系统所使用的串行数据通信技术也源于PC技术。之所以采用串行总线,是因为它们已在PC世界中得到验证,并导致价格的下降。图5表明超过70%的嵌入式系统开发者会考虑采用,或已经采用某种类型的串行总线,把它作为系统部件间的接口。

为观察这些串行总线设计中的关键信息流,工程师需要看到更宽的时间跨度。此外,用户还需要能隔离感兴趣的特定事件,这就要求有在串行数据流量中特定地址和数据上的触发能力。

传统浅存储器DSO可能具有捕获这些信号的带宽,但为观察整个数据包调整设置时,这些示波器不能保持其采样速度。图6是作为扫描速度函数的TektronixTDS3054B示波器和AgilentDSO6054A示波器的采样速度图。