2.4 采样与保持电路方案

采用射极跟随器、模拟开关和电容搭建采样与保持电路。射极跟随器可选用带宽稳定且带动容性负载强的运放,有较多的TI模拟开关,使其速度很容易满足要求,再选用合适的漏电小的聚苯电容即可实现采样与保持电路。

3 系统硬件电路设计

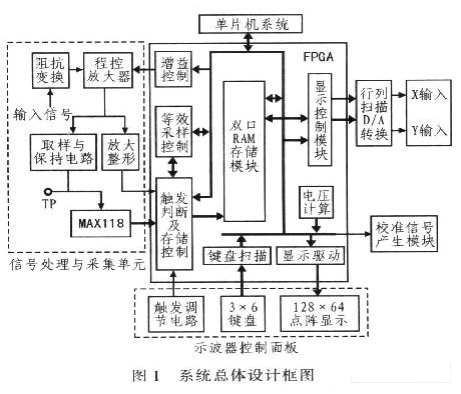

系统制定出系统总体方案:输入信号经阻抗变换电路后进行程控放大,再经采样与保持电路后进人MAX118进行采样。其中程控放大倍数和A/D采样速率由垂直灵敏度和水平扫描速度确定,采样时刻由上升沿触发判断和等效采样控制单元决定。采样数据存入双端口RAM,显示控制模块读取RAM内容并控制DAC904输出显示。图1为系统总体设计实现框图。

3.1 程控放大及前级阻抗匹配

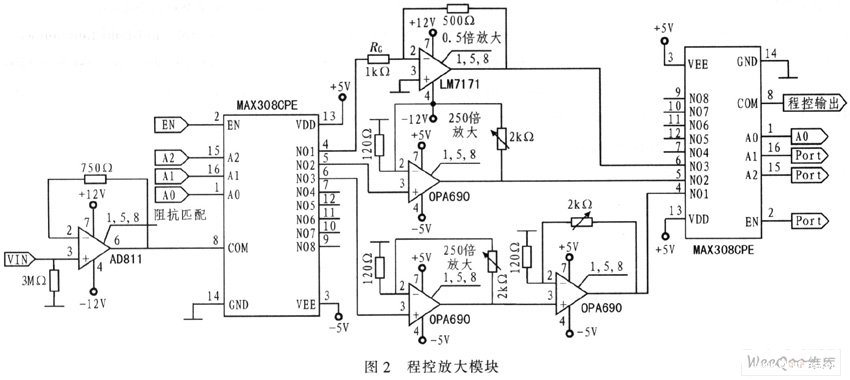

信号先经前级AD811的阻抗匹配后实现系统的输入阻抗为1 MΩ,再经过模拟开关MAX308CPE来实现不同通道放大的选择,最后经模拟开关COM总输出,如图2所示。

3.2 采样与保持电路

基于采样频带要达到10 MHz,系统采用模拟开关THS3166,其特点是低导通电阻、电容,低漏电流,低捕获时间和通断孔径时间,但只工作在正电压范围,故需前级加法器。开关前再加一级射极跟随器,采用带动容性负载强宽带运放THS3001做前后级的隔离。

3.3 整形及测频电路

高频段整形采用高速比较器MAX913,低频段采用低速比较器LM311。为提高输入MAX913信号的信噪比,在其前级加一级无限增益放大,采用高频率运算放大器LM7171,放大倍数50,这样减小MAX913输出脉冲边沿抖动。同时,为避免高频整形方波的谐波发射,比较器输出均经74LS393分频后送入FPGA进行等精度测频,脉冲边沿更陡峭,便于测量。