中断控制部件

L80C186-10能够从内部和外部的许多源接受中断,内部中断控制器把这些请求在一个优先级基础上进行合并,使其能由CPU一个一个地进行服务。内部中断源(定时器和DMA通道)能够被它们自己的控制寄存器或由在中断控制器中的屏蔽位来禁止。L80C186-10的中断控制器有自己的控制寄存器,该寄存器用于设置控制器的操作方式。

主设备方式下中断控制器的基本操作方式与8259A类似。中断控制器对在所有三种方式下的内部中断响应是相同的,不同的地方仅在于对4个外部中断引脚的功能解释上。中断控制器被设置到三种方式之一是通过对在INT0和INT1控制寄存器中的正确位进行编程来实现的。中断控制器的三种操作方式为全嵌套方式、级联方式和特殊全嵌套方式。

总线控制部件与L80C186-10指令集

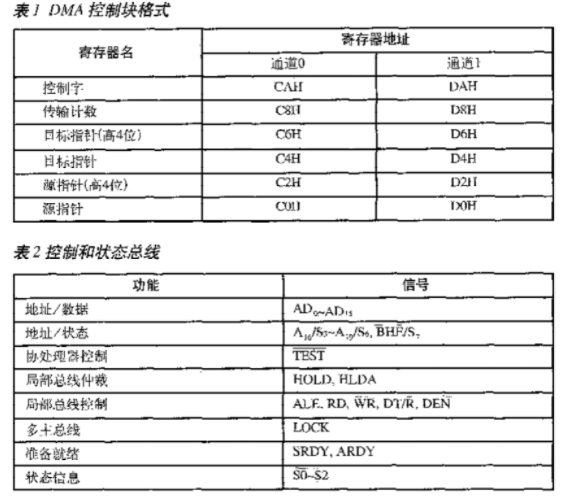

L80C186-10的总线接口与8086总线结构非常相似,它具有多路转换地址/数据总线,以及各种各样的控制和状态总线,每个总线周期需要最少4个CPU时钟周期和任意多个等待状态,其需要等待状态的个数由外部存储器和外部设备的访问速度所决定。

L80C186-10的指令集被分成7种类型:数据传送、算术、移位/环移/逻辑、串处理、控制转移、高级指令和处理器控制。一条80C186指令能够引用在任何地方的零个到多个操作数。一个操作数可以常驻在一个寄存器里,在指令本身中或在存储器中。

时钟发生器

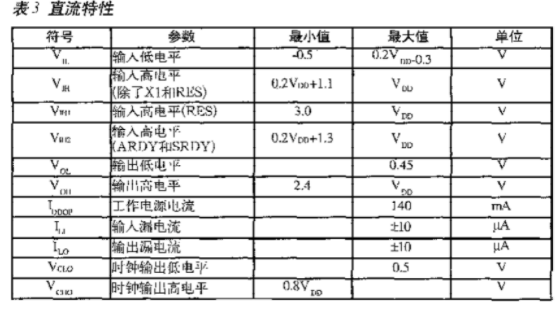

L80C186-10包含一个时钟发生器,用来为所有的L80C186-10集成部件,以及在该系统中所有与CPU同步的设备产生主时钟信号。这个时钟发生器包含一个晶体振荡器,二分频器,复位电路,以及准备就绪信号生成逻辑。