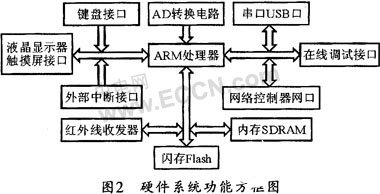

采用图2所示的结构进行设计可以最大程度地实现核心板的扩展功能。该设计在核心板上集成有ARM处理器S3CFS2410;内存63 M字节的SDRAM由两片K4S561632组成;10 MB的以太网控制器选用CS8900Q3;64 M字节的Nand Flash闪存选用K9F1208,而2MB的Nor Flash闪存则选用SST39VF1601。S3CFS2410是三星公司的一款基于ARM920T内核的16、32位RISC嵌入式微处理器,主要面向手持设备以及高性价比、低功耗的应用。它的运行频率可以达到203 MHz。此外,S3CFS2410集成的资源还包含有LCD控制器、SDRAM控制器、3个通道的UART、4个通道的DMA、4个具有PWM功能的计时器和一个内部时钟、8通道的10位ADC、触摸屏接口、IIS总线接口、2个USB主机接口、1个USB设备接口、2个SPI接口、看门狗计数器、117个通用I/O口和24个外部中断源、8通道的10位AD控制器、一个具有日历功能的RTC和具有PLL的芯片时钟发生器。由于该芯片用MPLL产生主时钟,因此能够使主处理器的工作频率高达203 MHz。

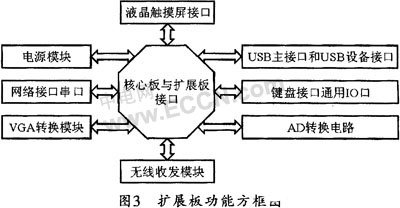

本设计在硬件实现方案上充分考虑到系统的可扩展性和核心板布局的灵活性,因而采用了拔插式的核心板布局。其他各外部功能处理模块(如键盘、模数转换电路、通用I/O口、液晶屏、触摸屏、网络接口、USB接口、无线收发模块、串口UART、VGA转化电路和电源模块)均采用扩展接口的形式来实现其模块功能,主要用来完成数据的收发、网络通讯、键盘操作以及图像处理和显示。通过这些特殊功能模块可对现场得到的数据进行特定的处理,以便很好地完成人机交互界面和通过外设对系统核心模块的控制,具体接口方式如图3所示。