2.4 USB2.0模块

为了降低数字信号中和器对PC硬件配置的要求和数字信号中和器本身的便携性,设计中采用USB2.0接口来实现数字信号中和器与PC问的数据传输。在气体检测的应用中,飞行时间质谱仪器中的离子飞行时间较短,每秒采样的数据量较少(为几十KHz),而利用集成USB2.0控制芯片CY7C68013可实现最高为48Mbyte/s的数据传输速度,故可以满足传输速度的要求。

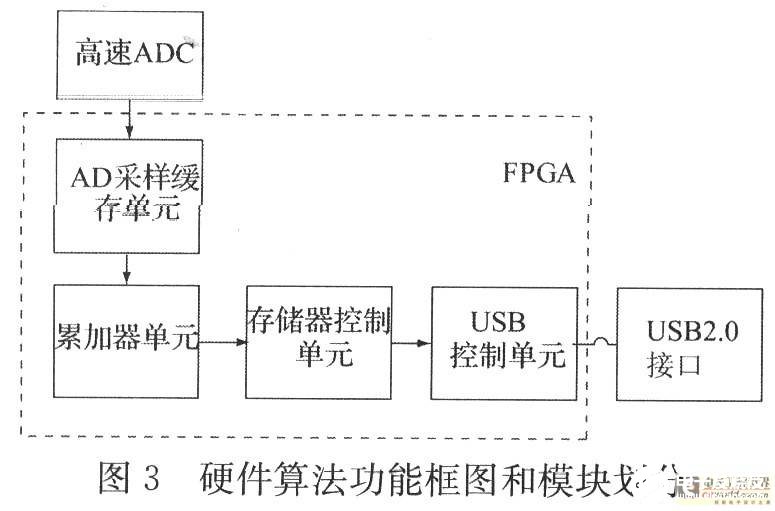

3 基于FPGA的数据处理

图3所示为数字信号中和器的FPGA硬件算法设计框图。设计中将硬件程序划分为AD采样缓存单元、累加器单元、存储器控制单元、USB控制单元。

3.1 A/D采样缓存单元

A/D采样缓存单元控制外部A/D芯片,并实现内部定时,每50us启动一次数据采集,每次数据采集持续时间20μs。并将采样数据存放在一深度为4的缓存中,缓存中的数据由累加器单元进行后续处理。

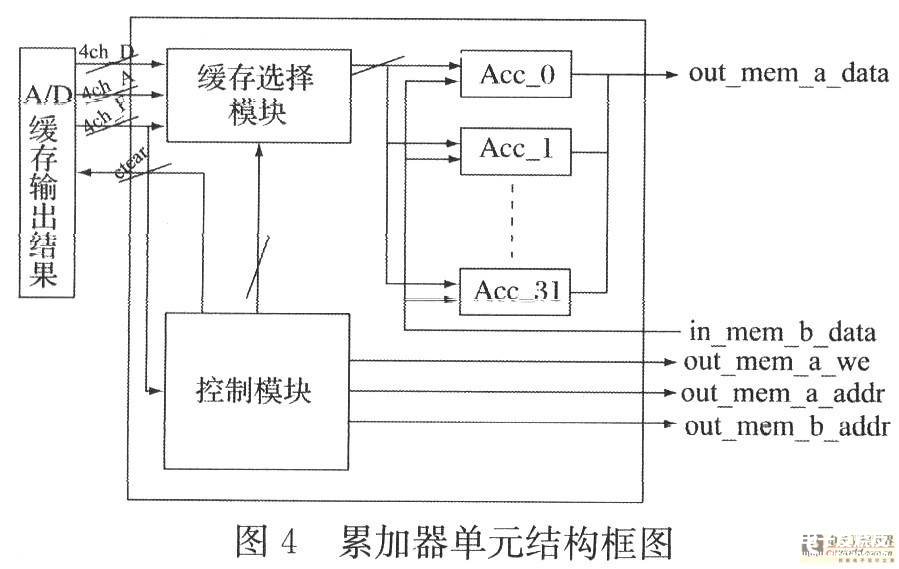

3.2 累加器单元

图4所示为累加器算法流程。当A/D采样缓存单元中的缓存有数据时,读取缓存中数据,一次读取32个采样点,将采样结果和存储器中对应地址的数据相加,并将累加再次写入存储器中的对应地址。

3.3 存储器控制单元

图5所示为存储器算法流程。存储器控制单元内部包含了两个存储体。任一时刻,两个存储体分别由累加器单元控制,实现数据累加;或由USB控制单元控制,将存储体中的数据传输至上位机。由存储器控制单元进行控制,两个存储器进行乒乓操作,每秒进行一次切换,即每秒完成一浓累加循环。