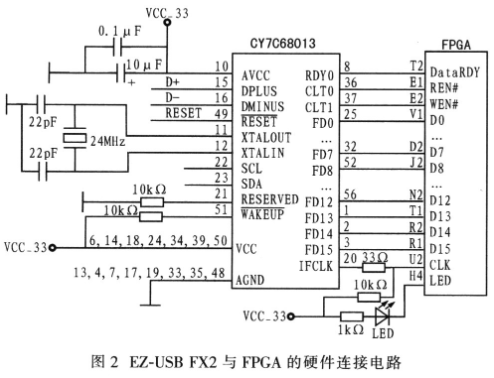

3 系统结构

系统结构框架如图1所示。通过导联由人体采集到的心电、脑电、肌电等信号调理电路后,由FPGA内部逻辑控制A/D转换对其采样。将经采样并通过A/D转换后的数据暂时缓存到EZ-USB FX2的内部FIFO中,供PC机读取。整个系统涉及A/D转换及其通道选择、信号放大、FPGA控制和EZ-USBFX2接口设计,这里主要介绍EZ- USB FX2接口设计,以及相应固件程序的开发与GPIF波形设计。

4 器件资源分配

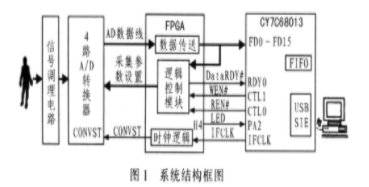

4.1 EZ-USB FX2与FPGA的硬件连接

EZ-USB FX2采用GPIF接口和FPGA相连,其硬件连接电路如图2所示。EZ-USB FX2与FPGA连接的引脚分配如下:FD0~FD15为GPIF双向数据线,负责读写数据:CTL0、CTL1分别为读(REN#)、写(WEN#)使能信号;RDY0为FPGA发出的数据准备好信号;PA2与FPGA的H4引脚连接,用于数据采集开始时点亮LED。

4.2 端点分配

系统中数据通道分为数据上传通道以及配置和控制命令通道,根据设计需要,选择其中两个端点分别作为发送和接收端点。配置如下:EP2用于从USB向FPGA传输采集控制命令,4×512字节缓冲,传输类型为批量OUT传输方式;EP6用于从 FPGA向USB传输数据采集结果,4×512字节缓冲,传输类型为批量IN传输方式。EZ-USB FX2相当于一个中转站,一方面将FPGA发来的采集数据传输给主机,另一方面将主机发送的数据采集参数传输至FPGA,便于控制A/D转换。