式中Pr为行地址的奇偶性,Pc为列地址的奇偶性。

FLASH芯片奇偶性图形功能检测的流程是:首先根据算法写入背景图形,然后逐位读出并检验结果的正确性,再将芯片数据擦除,以反码图形重复上述测试过程。其总的测试步数为M=4N。

由于奇偶性图形是不对称的,任何一位的地址译码器失效都会引起本应写入互为反码数据的两个存储单元之一重复选址,并且第二次选址改变了第一次选址时写入的内容,而另一个存储单元未被访问。因此地址奇偶性图形可以很好地检验出地址译码器的故障。

奇偶性图形每次都把整个存储器单元写完后再整体读出,没有反复擦除的过程(整个过程只需擦除两次),非常适用于FLASH芯片测试。

4.2 齐步法

齐步法[6]是对存储器的每个单元依次进行检验的一种方法。首先从第一个存储单元开始,逐个对每个单元进行取反和检验,直到最后一个单元检测结束才完成一遍扫描。然后,在背景为反码的情况下,从第一个存储单元开始,逐个对每个单元进行取反和检验,直到最后一个单元检测结束。整个过程就像所有单元一起向前走步一样,因此称为“齐步法”。根据FLASH芯片特点,我们改变在反码背景条件下走步的过程,把它改造如下,形成了适合的齐步算法。

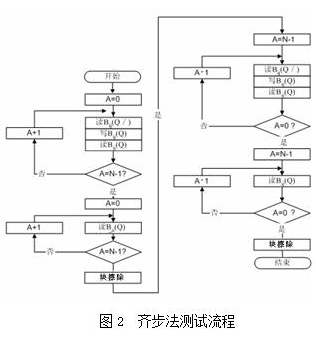

在图2中给出了测试FLASH齐步法的测试流程:

在测试之前,每个存储单元具有信息“1”。首先在存储矩阵中写入背景图案(初始状态为全“1”),然后从地址A0开始选址进行读“1”,写“0”,读“0”操作,并检验读出结果。接着,依次到下一个选址单元重复该操作(读“1”,写“0”,读“0”),直到全部存储单元(A=N-1)重复完为止。再在读操作方式下对全部存储单元进行一次正向扫描读出,检查有无正向对反向的多重写入问题。然后将存储器输入擦除,使之全部单元为全“1”。进而开始反向扫描:从最高地址AN-1开始执行读“1”,写“0”,读“0”操作,逐位进行上述操作过程,直至最终地址为AN-1,最后对全部存储单元进行读“0”扫描,以检验读出结果的正确性。