如果采用市面上通用的MIL-STD-1553总线控制芯片,无法实现上述的总线故障注入功能,同时也没有商用的带有故障注入功能的总线控制芯片出售。所以为了能够实现上述功能,测试设备开发商需自行开发带有故障注入功能的1553总线控制芯片。

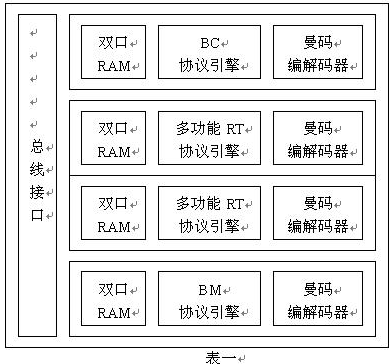

基于上述考虑,矽微公司自行开发了总线测试设备专用的1553总线控制IP核,可以在ACTEL和ALTERA的多个系列的FPGA实现。用于采用硬逻辑的方式来注入故障,所以改IP核能够实现标准所规定的全部故障注入功能。此IP核的功能框图如表一:

如表一所示,控制器IP核中实现了一个BC、一个BM和两个多功能RT,这些功能可以同时工作,并且可以同时仿真32个RT。IP核采用64M时钟,可以以15.6ns的分辨率在总线上注入过零点偏差,大大提高了总线测试的精度。经过矽微公司数个型号的总线测试设备的验证,证明这个IP核的设计是合理的,工作状态是稳定可靠的。

如果只实现1553控制器的IP核,还是无法实现总线的自动测试的。除总线控制器外,还需实现示波器的采样逻辑,信号发生器的逻辑以及时域反射计的逻辑。同时还要根据总线测试标准的要求,将这些逻辑组合起来,以方便总线电气性能的测试。AT15000采用ALTERA公司的CYCLONEIII FPGA芯片,在FPGA中实现了上述几种逻辑。其中的示波器逻辑可以由1553控制器的逻辑来触发,使得总线电气特性的测试变得非常简单。

作为ATE,总线测试设备需要具备较高的自动化程度,尽量减少人工干预。所以在设计测试仪软件的时候,需要仔细分析测试标准,将测试项目分类并细化成若干个子测试项目,让用户可以自由选择测试项目并定义测试顺序,以使测试更加灵活,进而满足不同测试场合的需要。AT15000根据总线终端设备类型将测试分为RT测试、BM测试和BC测试三种,同时将每种测试分为很多个子测试项目,用户可以通过脚本的形式来自由选择测试项目和定义测试顺序。在三种类型的测试中,除了RT的测试之外,BM和BC的测试需要受测设备的软件配合,所以在测试BM和BC的时候,用户需要编写受测设备的软件,用以配合测试仪的测试。