(1) 实际闸门对标准频率的随机性导致计数值NB的±1误差是主要误差。

(2) 时钟脉冲产生的标准频率F0的稳定度产生的测量误差。时钟脉冲由晶体振荡器产生。由于目前晶体振荡器主要分为温补晶体振荡器和恒温晶体振荡器两大类,其中,温补晶体振荡器体积小,开机时间短,稳定度一般在10-7数量级以上。而恒温晶体振荡器的稳定度更高,因而相对于量化误差,标准频率误差可以忽略。公式(6)就是在忽略标准频率误差的情况下得到的。由于分频系数为8,则测频精度为1/(8×65 536)=1.907e-6。若要进一步提高频率测量的精度则可以增加分频系数。

4、CPLD设计

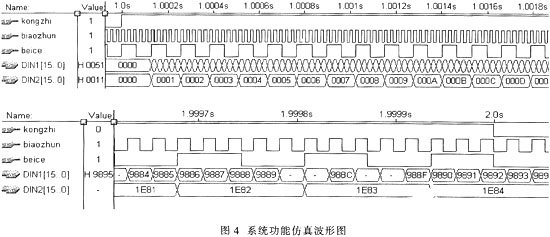

本系统设计采用Altera公司生产的CPLD器件EPM7128实现其中的逻辑部分。用MAXPLUS+11软件工具开发,采用Verilog语言编程。设计输人完成后,进行整体的编译和逻辑仿真,然后进行转换、布局、延时仿真生成配置文件和下载文件,最后下载至EPM7128器件,实现其硬件功能。仿真波形如图4所示,其参数为:beice=8 MHz,biaozhun=50 MHz。结果表明各信号的逻辑功能和时序配合都达到了期望指标。不同被测频率的仿真值如表2所列。

5、结束语

本频率计的设计将MSP430单片机的计数器Timer_A和Timer_B均设置为计数方式,比以往一个定时/计数器作定时器,另一个定时/计数器作计数器的方式计数精度要高,并且测量精度与被测信号无关,实现了0 MHz~10 MHz频率范围内的等精度测量,智能闸门控制方式使测量方便、灵活。本频率测量系统还能实现更高频率测量范围的等精度测量,这时要根据不同测量系统的要求选择24位、32位计数器。