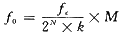

信号发生器输出波形的频率f0定义为:

其中fc为晶振频率,k为分频比,N为相位累加器位数,M为相位累加器的增量(步长)。

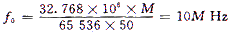

本设计中取fc=32.768 MHz,k=50,N=16,代入上式可得:

这样只要控制M的值就可以准确地实现频率步进10Hz的要求。这里时钟频率为:

式中,△phase为频率控制字,sysclk为系统时钟,clkin为DDS的输入参考时钟频率,N为频率寄存器的位数,M为相位偏移寄存器的位数。频率控制字△phase决定着输出信号的频率值;最小频率分辨率由频率寄存器的位数N决定,N越大,频率分辨率越高;相位分辨率由相位偏移寄存器的位数决定,幅度分辨率由D/A转换器的精度决定。

2.2 幅频和相频特性设计

幅频特性测试电路由峰值检波器和D/A转换器组成。峰值检波器由“运放”和检波二极管构成。如图3所示。他将被测网络的输出信号峰值检出来(代表网络幅频规律),送往8位ADC0809模数转换器,数字化后再送单片机AT89C51进行处理。

幅频特征测试中常用的检波方式有峰值检波和有效值检波。但由于有效值检波无法达到设计要求的500 Hz~10 kHz频率变化范围,所以采用峰值检波。利用有源峰值检波器实现峰值测量,峰值检波器将被测网络的输入和输出信号的峰值检出,再送至A/D转换器完成量化。实际上,由于信号源的D/A及低通滤波器的特性能保证在100 Hz~100 kHz范围内的幅值保持不变,所以可以省去一路峰值检波器及A/D,而只采集被测网络的输出信号。