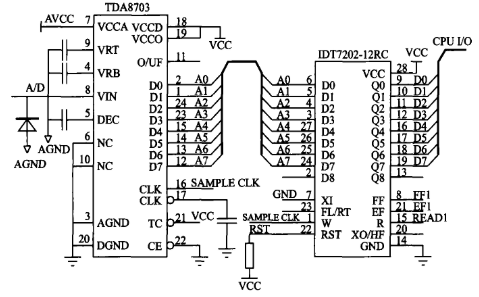

TDA8703的采样时钟与IDT7202的写信号接同样一个时钟,这样便使两者同步。当采样1 024个点时,关闭采样时钟信号,IDT7202的FF端低电平有效,CPU把IDT7202中的数据取出并查询IDT7202的空标志位端;当低有效时,意味着IDT7202中的数据全部被取出,这时重新开采样时钟信号,重复上一过程。

由于本设计显示采用的是PC机,受到串口上传波特率的限制,所以很难实现高频信号的测量,而上述设计恰恰在一定程度上解决了这个问题。由于1 024个采样点是连续的,可以逐步上传而形成完整的波形。但是,把1 024个采样点上传给PC机的过程中ADC是禁止采样的,所以在PC机上看到的波形有不连续的“接头”。不过,这对于简易的数字存储示波器是可以“容忍”的。

在设计的过程中,由于走线过多,所以即使试验阶段也得做PCB板;但是由于各芯片间的控制逻辑不确定,很容易出错。这时采用CPLD来搭建此系统的逻辑电路,一旦出错,可以随时修改,直到正确。如果整个系统调试成功后,用与、或、非等逻辑电路替换CPLD,这样可降低成本。

3 、信号传输模块

本设计负责信号传输的CPU是C8051F020。C8051F系列单片机是完全集成混合信号的系统级芯片,具有与8051兼容的控制器内核,与MCS-51指令集兼容;除具有标准8051的数字外设部件外,片内还集成了数据采集和控制系统中常用的模拟部件和其他数字外设及功能部件。C8051F单片机采用流水线结构,机器周期由标准的12个系统时钟降为1个系统时钟周期,处理能力大大提高,峰值性能可达25 MIPS。