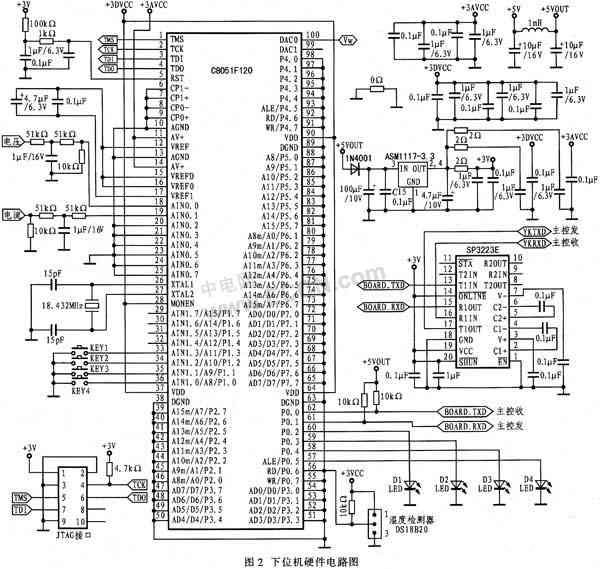

下位机硬件设计电路主要由高性能C8051F120单片机、A/D转换接口电路、人机接口电路、串口通讯电路、电源电路、系统复位电路、A/D转换电压基准电路、外部时钟电路、JTAG接口电路等组成。其硬件电路图如图2所示。

2.1.2下位机各模块设计

(1) C8051F120单片机

C8051F120单片机是完全集成的混合信号片上系统SoC(System on Chip)级MCU器件,具有与MCS-51内核及指令集完全兼容的高速、流水线结构。机器周期由标准的12个系统时钟周期降为1个系统时钟周期,峰值可达25 MI/s。除了具有标准8051的数字外设部件之外,片内集成了数据采集和控制系统中常用模拟器件和其他数字外设及功能器件,两个全双工增强型串行通讯接口(UART),真正12位、100 Ks/s逐次逼近型(SAR)8通道ADC,完全能够满足高速、高精度、多通道数据采集,数字滤波,数据传输的需求。此外,片内还集成基于JTAG协议的调试电路,通过JTAG接口可实现对C8051F120单片机闪存的读写操作,以及全速、非侵入式在系统调试。

(2) A/D转换接口电路

C8051F120单片机的ADC0~ADC1子系统各通道输入电压应小于等于基准电压,传感器信号多为微弱电流信号,根据信号采集传感器的特点,需在通道接口设计传感器信号处理电路、电压转换电路和插拔式接口。

(3)人机接口电路

C8051F120单片机为100引脚TQFP封装,具有标准8051的端口,还具有附加的4个8位I/O端口,这样无需接口器件拓展I/O端口,采用在P0.2~P0.5 I/O端口连接发光二极管,采用共阴极方式设计D1~D44个工作状态指示灯,在P1.0~P1.3 I/O端口使用按键开关设计KEY1~KEY4.4个数据采集系统控制按键,实现数据采集、数字滤波和数据传输功能。