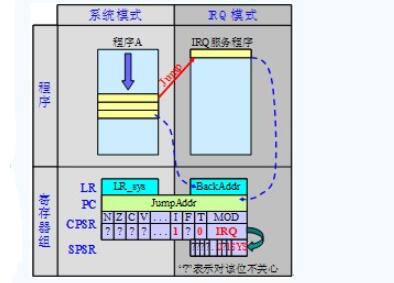

(1)将CPSR寄存器内容存入IRQ模式的SPSR寄存器

(2)置位I位(禁止IRQ中断)

(3)清零T位(进入ARM状态)

(4)设置MOD位,切换处理器模式至IRQ模式

(5)将下一条指令的地址存入IRQ模式的LR寄存器

(6)将跳转地址存入PC,实现跳转

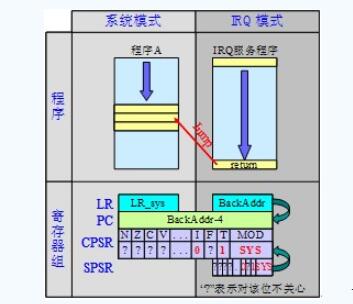

图示“退出异常”过程:

在异常处理结束后,异常处理程序完成以下动作:

(1)将SPSR寄存器的值复制回CPSR寄存器;

(2)将LR寄存的值减去一个常量后复制到PC寄存器,跳转到被中断的用户程序。

下面讲讲“快速中断请求”:快速中断请求(FIQ)适用于对一个突发事件的快速响应,这得益于在ARM状态中,快中断模式有8个专用的寄存器可用来满足寄存器保护的需要(这可以加速上下文切换的速度)。

不管异常入口是来自ARM状态还是Thumb状态,FIQ处理程序都会通过执行下面的指令从中断返回: SUBS PC,R14_fiq,#4

在一个特权模式中,可以通过置位CPSR中的F位来禁止FIQ异常。

关于“中断请求”:中断请求(IRQ)异常是一个由nIRQ输入端的低电平所产生的正常中断(在 具体的芯片中,nIRQ由片内外设拉低,nIRQ是内核的一个信号,对用户不可见)。IRQ的优先级 低于FIQ。对于FIQ序列它是被屏蔽的。任何时候在一个特权模式下,都可通过置位CPSR中的I 位来禁止IRQ。