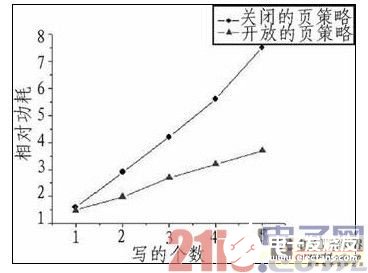

图1 开放的页策略和封闭的页策略的功耗比较

根据上面对SDRAM功耗的特点的分析可知,尽量减少激活/关闭存储体引起的附加功耗开销,是优化SDRAM存储系统功耗的根本,另外不能忽视一直处于激活状态的存储体带来的功耗。

2 访问SDRAM的低功耗优化设计方案

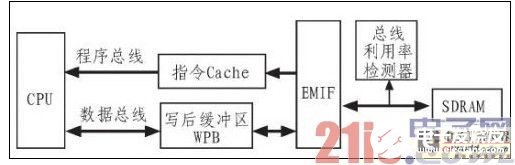

为更好的管理外部SDRAM,大部分嵌入式DSP片上集成和外部存储器的接口EMIF(External Memory Interface),DSP的片内设备通过EMIF访问和管理存储器。由EMIF将对同一行的读写尽量归并到一起进行,减少激活/关闭存储体引起的附加功耗开销。图2为基于总线监测的读写归并设计方案的框图。

图2 基于总线监测的读写归并设计方案的框图

1)采用块读的方法取指令。加入简化的指令Cache(I-Cache),将对SDRAM的读程序读操作按块进行。只有在Cache错过时,由Cache通过EMIF对SDRAM进行块读,每次读16个字节。

2)加入写后数据缓冲区(WPB,Write PoST Buffer),将数据总线上的请求发往WPB,由WPB对SDRAM进行块写、读写归并。

3)动态监测EMIF总线的利用率,块读和读写归并时采用开放的页策略,当总线利用率较低时,采用封闭的页策略,当总线利用率很低时,将SDRAM进入休眠模式。

3 访问SDRAM的低功耗设计

3.1 采用块读的I-Cache

对于程序总线的读操作,根据程序的局部性原理,下一次要取得指令和当前要取指的指令在空间上很可能相邻,因此对于读程序采用块读的方法,每次读一个块,而不是一个字,并采用开放的页策略,因此对同一行的读写操作不需要额外的激活/关闭操作,可以较快的完成。