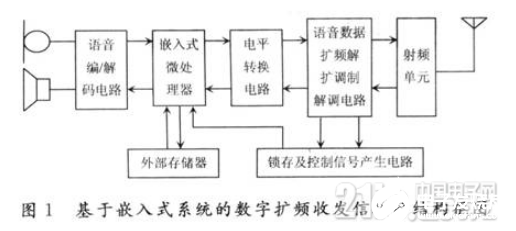

设计的基于嵌入式系统的数字扩频收发信机结构框图如图1所示。

该数字扩频收发信机是双通道的(图中只画出单一通道)。通道由语音编解码电路、嵌入式微处理器、电平转换电路、语音数据扩频解扩调制解调电路、锁存及控制电路、外部存储器和射频单元电路组成。

语音编解码电路采用PHLIPS半导体公司生产的低功耗立体声音频编解码芯片UDAl344TS。该芯片3.O V电源供电,可工作在L3微控制器模式,也可工作在静态引脚工作模式,通过模式控制引脚MCl(8脚)、MC2(21脚)设置为静态引脚工作模式(均为高电平),在该模式下,可控制的特征有系统时钟选择、数据输入/输出格式设置、重低音和静音控制以及ADC控制,这些特征是由引脚MPl(9引脚)、MP2(13引脚)、(14引脚)、(15引脚)、MP5(20引脚)控制的。

嵌入式微处理器选用公司为手持设备设计的低功耗、高集成度基于ARlM920T核的微处理器。该处理器集成了16 KB指令和16 KB数据缓存、MMU、外部存储器控制器、控制器、NAND 控制器、4个DMA通道、3个通道、1个I2C总线控制器、1个I2S总线控制器、4个PWM器和一个内部器、通用I/O口、实时时钟、8通道10位ADC和接口、USB主/从接口、SD/MMC卡接口等。

语音数据扩频解扩调制解调电路选用公司研制的可编程单片直接序列扩频收发芯片Z87200。该芯片包括发送部分、接收部分和控制部分,它将扩频通信收发主要电路的各个部分都集成于一块100个管脚的芯片中。发送部分包括了发送数据的白化处理、串并变换、差分编码、PN码产生、扩频、QPSK/调制及发,完成由数据输入到已调中频信号输出的扩频、调制处理。接收部分包括中频到基带的数字下变换、PN码产生、数字匹配滤波、解扩、相关峰检测、差分解调、并串转换、去白化处理、数控振荡器及位定时处理等,完成由数字中频信号输入到数据输出的全过程解调解扩处理。此外,Z87200还设置了86 B的片内寄存器,用于对芯片功能的编程设置,使得对扩频系统的设置具有灵活性,芯片具有通用性,可与计算机或单片微处理器连接,完成对内部寄存器的编程控制。