2.2 硬件实现

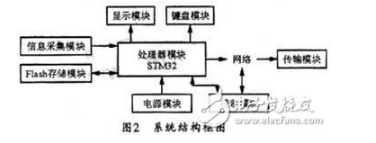

本系统的处理器模块选用ST公司刚刚推出不久的、基于ARM CortexTM-M3内核的新一代嵌入式STM32芯片。这是一款专为嵌入式应用而开发的内核。它带有把中断之间延迟降到6个CPU周期的嵌套向量中断控制器,允许在每一个写操作中修改单个数据位的独立位操作,可进行分支指令预测、单周期乘法、硬件除法且有高效的Thumb 2指令集。这些改良技术使Cortex-M3内核具有优异的代码密度、实时性和低功耗性能。所有这些新功能都同时具有目前最优的功耗水平,非常适合应用于长时间工作的终端控制系统。

本系统由+12 V电源输入,同时经过LM2575和78L09稳压后分别得到5 V和9 V电压,5 V再经过SPX1117M3-3.3电压稳压转换后得到3.3 V,这样3.3 V、5 V和9V电压即能够很好地满足内核、外设和外部电路的供电。系统时钟源可采用外部晶振,内部PLL电路可以调整系统时钟,使系统运行速度更快。为了提供性能优越的电源监控性能,这里选取了专门的MAX811系统监视复位芯片,该芯片可以通过手动控制系统的复位,同时还可以实时监控系统电源,一旦系统电源低于系统复位阀值,电路中的MAX811将产生一个140ms的复位脉冲信号来对系统进行复位。

系统网络模块选用的W5100芯片是一款多功能的单片网络接口芯片。它内部集成有10/100Mbps以太网控制器,可支持自动应答(全双工/半双工模式),主要用于高集成、高稳定、高性能和低成本的嵌入式系统。使用W5100可以实现没有操作系统的Internet连接。W5100与IEEE802.310BASE-T和802.3u 100BASE-TX兼容。此外,W5100内部集成有全硬件的、经过多年市场验证的TCP/IP协议栈、以太网介质传输层(MAC)和物理层(PHY)。其硬件TCP/IP协议可支持TCP、UDP、ICMP、IGMP、IPv4、ARP、PPPoE和IGMP。同时可支持4个独立的端口(Socket)通信,其内部16 K字节的发送,接收缓冲区可快速进行数据交换,其最大通信速率可达25 Mbps。利用W5100提供的多种总线(并行总线和SPI总线)接口方式可以很方便地与各种MCU连接。可以说,W5100器件的推出,大大简化了硬件电路设计,并可使微控制器系统在没有操作系统的支持下实现单芯片接人Internet的理想。一般情况下,只需设置寄存器和存储器,就可以通过W5100芯片进行Internet奎接。

在设计中,STM32F103与W5100可通过SPI接口进行连接。STM32F103作为SPI主设备,W5100作为SPI从设备,并由STM32F103为W5100提供通信时钟,二者的接口连接图如图3所示。