SDRAM存储器布局

当使用SDRAM时,外部存储控制器(EMC)分配SDRAM一定的地址空间。开发者可以使用链接描述文件将代码或数据分配到SDRAM中。值得注意的是,链接器脚本编程在不同IDE之间是不同的。

以LPC5460x系列微控制器为例,SDRAM支持4个片选区,每个片选区最大支持256MB空间。

SDRAM片选地址范围

00xA0000000 - 0xA7FFFFFF

10xA8000000 - 0xAFFFFFFF

20xB0000000 - 0xB7FFFFFF

30xB8000000 - 0xBFFFFFFF

当SDRAM的硬件连接使用SDRAM片选0的情况下,在KEIL平台下,将加载在SPI FLASH的Coremark基准测试程序拷贝到SDRAM中执行需要以下几步。(coremark基准测试程序包括core_list_join.c,core_matrix.c,core_state.c及core_util.c)。

定义SDRAM区域,从0xA0000000开始,大小为0x80000。定义SPI FLASH区域,大小为0x80000(SPI FLASH存储器的起始地址为0x10000000)。

在C源码中使用“SDRAM_Data” 和 “SDRAM_Function”属性,标记放在SDRAM区域中的数据或程序。(SDRAM_Data和SDRAM_Function只是文本名字)。

也可以将整个目标文件的数据和程序段配置到SDRAM

# definem_spifi_start 0x10000000 # definem_spifi_size 0x800000 # definem_sdram_start 0xA0000000 # definem_sdram_size 0x80000 LR_m_text2 m_spifi_start m_spifi_size { ; load to SPIFI LR_m_sdram_text m_sdram_start m_sdram_size { *(SDRAM_Data) *(SDRAM_Function) core_list_join.o core_matrix.o core_state.o core_util.o }

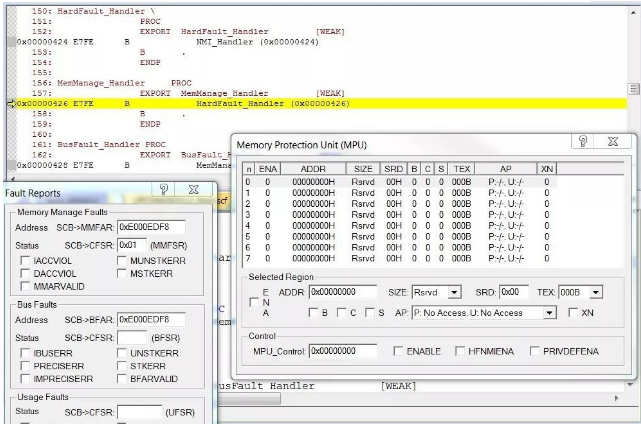

配置MPU

在SDRAM中运行程序,开发者可能需要配置ARM内核内存保护单元(MPU)。

内存保护单元(MPU)是一个可编程单元,用于定义内存访问权限。当MPU没有使能时,内存地址空间具有默认的访问权限。

如ARM Cortex™-M4器件通用用户指南中所述,当程序执行SDRAM中的代码且SDRAM内存影射地址的默认属性为禁止执行时, 内核就会产生HARDFAULT异常,且指令访问冲突标志SCB-》CFSR为 1,该异常表示处理器尝试从不允许执行的位置获取指令。

因此,当SDRAM被影射到默认不可执行的地址空间时(如在LPC5460x中,SDRAM影射到0xA0000000起始的地址),开发者必须配置并使能MPU才能在SDRAM中执行代码。如下例中,代码配置并使能MPU,允许从0xA0000000到0xA0100000的内存区域是可执行的。

MPU-》RNR = 0; //Region number 0 MPU-》RBAR = 0xA0000000; //Region base address/* Full Access | TEX: 000 | S: 0 | C: 0 | B:0 (No cacheable, no shareable)| 1M SIZE | ENABLE */ MPU-》RASR = ( 0《《 28) | ( 0x3《《 24) | ( 0x0《《 19) | ( 0《《 18) | ( 0《《 17) | ( 0《《 16) | ( 0xFF《 8) | ( 0x13《《 1) | ( 1《《 0); //Region size and enable MPU-》 CTRL= MPU_CTRL_ENABLE_Msk| MPU_CTRL_PRIVDEFENA_Msk;