1 系统整体方案设计

针对高压大功率电力电子设备的安全可靠性要求较高、控制算法较为复杂、控制与检测信号量较多等特点,本文以 DSP+FPGA+CPLD 为核心,结合高性能外围器件和高速接口,设计了一种主控制器与外围插件板分离的硬件方案。

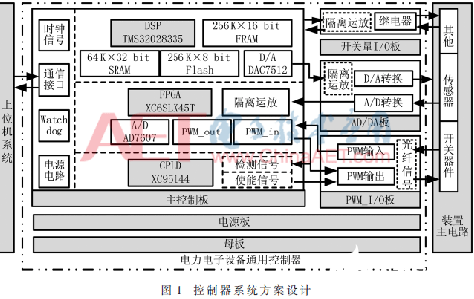

该系统集高速算法运行、快速输入输出接口、多时间尺度控保融合于一体,对不同结构和功率等级电力电子装置的算法执行、继电保护配置都有较强的适应性。基于 DSP+FPGA+CPLD 的电力电子设备通用控制器系统方案如图 1 所示。

2 系统硬件设计方案

2.1 系统主要器件选型

控制器系统选用高性能器件提高电力电子设备控制的高效性和安全可靠性,同时结合拆分板块的结构设计增加系统应用的通用性。其中,DSP 采用 TI 公司的高速浮点型芯片 TMS32028335,其具备最高 150 MHz 主频、32 位高精度浮点处理单元、6 通道直接存储器访问通道(DMA)、充足的 RAM 和 Flash 存储容量、程序与数据分离的哈佛流水结构,可以满足大多数电力电子设备的算法运算需求;FPGA 采用 Xilinx 公司 Spartan6 系列的 XC6SLX45T,其拥有 43 661 个逻辑单元、54 576 个触发器、最大 358 个用户 I/O 引脚数、最大 2 088 Kb 的 Block RAM 模块,方便实现接口扩展与采样控制;CPLD 选择 Xilinx 公司的 XC95144,其包括最快 111 MHz 的时钟频率、最大 133 个用户 I/O 引脚、7.5 ns 的管脚相对延时、片内编程信息断电不丢失等特点,能够较为可靠地完成电力电子设备 PWM 信号的检测与故障闭锁功能;AD 采样芯片采用 Analog Device 公司的 AD7606 芯片,其参数为:8 通道 16 位采样精度和 200 kS/s ADC,可以满足绝大部分电力电子设备的信号采样精度需求。

2.2 系统板块功能介绍

由图 1 可知,控制器主要分为包含 DSP、FPGA 和 CPLD 的主控制板,PWM 输入和输出的 PWM_I/O 板,A/D 转换和 D/A 转换的 AD/DA 板,开关量输入和输出的开关量 I/O 板,包含多个开关电源模块的电源板,以及负责上述各个板块间连接的母板几部分。其中,各个功能板块电路模块设计固定,除主控制板、电源板和母板外,PWM_I/O 板、AD/DA 板、开关量 I/O 板均可根据控制对象需求进行板块数量增加。

主控制板为整个控制器核心。其中 DSP 及其相应外围电路实现复杂控制算法执行、事件记录、与上位机通信、D/A 转换输出以及部分开关量输入输出等核心控制与系统级保护功能;FPGA 及其相应外围电路主要控制高速 A/D 采样与转换、PWM 信号的发生以及 PWM 信号的输出与接收等器件级控制功能;CPLD 及其相应外围电路完成对 FPGA 产生的 PWM 信号的高速检测,并在 PWM 信号输出正确时输出使能信号完成 PWM 信号向开关器件的传输,否则闭锁 PWM 信号输出,并向 FPGA 和 DSP 进行反馈,FPGA 停止 PWM 信号发生和输出,DSP 进行事件记录并输出告警信号。主控制板是整个控制器实现对电力电子设备的多时间尺度控保融合的核心板块。图 2 所示为控制器控保融合方案设计。