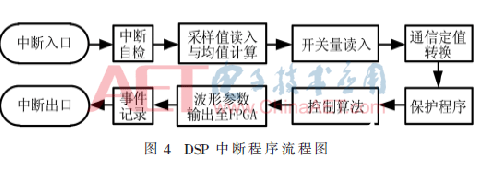

中断程序主要完成中断自检、对来自 FPGA 的 AD 采样值读入与平均值计算、开关量读入、通信定值转换、保护程序执行、控制算法运算、波形参数(占空比或正弦波)输出以及事件记录。中断程序的执行周期可根据实际设备需求进行修改。DSP 中断程序流程如图 4 所示。

3.2 FPGA 软件设计

FPGA 软件主要为基于多时钟频率下并行处理的高速 AD 采样控制和 PWM 信号的输出全数字化实现。

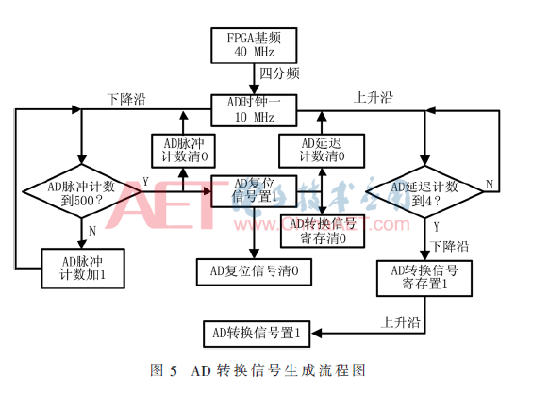

基于芯片 AD7606 采样转换时序的 AD 采样控制主要包括 AD 同步信号生成、AD 复位信号生成、AD 转换信号生成、AD 转换完成信号输出、AD 信号读取等流程。图 5 所示为以 FPGA 主频 40 MHz、10 kHz 采样频率为例的 AD 转换信号生成流程图。

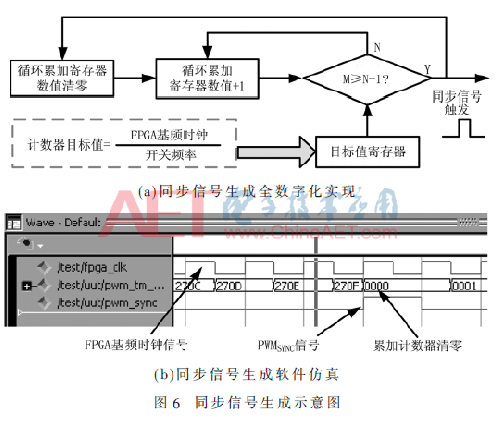

PWM 信号输出数字化实现方法为:利用计数器累加完成同步信号 PWMSNYC 的发生,同步信号的频率为电力电子设备的开关频率。同步信号的数字化生成及其软件仿真结果如图 6 所示。

3.3 CPLD 软件设计

CPLD 软件主要是对 FPGA 生成的 PWM 信号进行高速检测,并在故障时进行闭锁。具体实现方法为:FPGA 在产生 PWM 信号输出时,同时作为 CPLD 的输入信号,CPLD 程序对输入信号进行高速逻辑判断:若判断输入信号正常,则输出使能信号,完成 PWM 信号向开关器件的输出;否则输出闭锁信号,闭锁 PWM 信号输出,并向 DSP 和 FPGA 输出告警信号。

4 实验验证与结果分析

为验证本设计的可行性,在大型矿车制动能量回收与利用装置(以下简称“该装置”)上运用了本控制器。

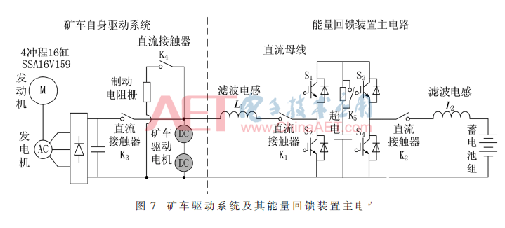

该装置是利用双向 Boost-Buck 变换电路结合超级电容和蓄电池实现矿车制动能量的回收的节能装置。图 7 所示为矿车驱动系统与该装置主电路拓扑结构图。