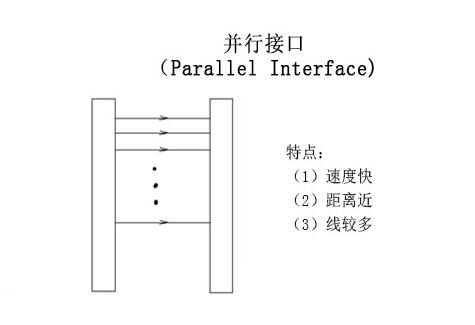

当处理器选择的地址位于设备指定范围内的时候,译码电路对芯片选择线进行触发,从而激活设备。然后,处理器可以使能相应的控制线(分别是RD\与WD\),从而由设备读出数据,或者是向设备写入数据。为了实现并行通信,系统需要严格遵循时序规范。前面已经提到过,并行通信是由主控处理器启动的。如果某外围设备想要对通信进行初始化,那么可以向处理器发出中断,告知相关信息。为了实现上述功能,设备的中断线需要连接到处理器的中断线上,并且主控处理器需要触发相应的中断。需要说明的是,主控处理器的数据总线宽度决定了并行接口的宽度,可以是4位、8位、16位、32位、64位等。设备支持的总线宽度应该与主控处理器完全相同。并行数据通信为系统提供了高速数据传输能力。

关于接口,总线,驱动就介绍完了,您有什么想法可以联系小编。